AD8328ACP-REEL Analog Devices Inc, AD8328ACP-REEL Datasheet - Page 10

AD8328ACP-REEL

Manufacturer Part Number

AD8328ACP-REEL

Description

IC LINE DRIVE CBLE 5V 20LFCSP TR

Manufacturer

Analog Devices Inc

Type

Line Driver, Transmitterr

Datasheet

1.AD8328ARQZ.pdf

(20 pages)

Specifications of AD8328ACP-REEL

Rohs Status

RoHS non-compliant

Applications

Modems, Set-Top Boxes

Mounting Type

Surface Mount

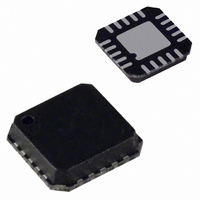

Package / Case

20-LFCSP

AD8328

APPLICATIONS

GENERAL APPLICATIONS

The AD8328 is primarily intended for use as the power

amplifier (PA) in Data Over Cable Service Interface Specification

(DOCSIS)-certified cable modems and CATV set-top boxes.

The upstream signal is either a QPSK or QAM signal generated

by a DSP, a dedicated QPSK/QAM modulator, or a DAC. In all

cases, the signal must be low-pass filtered before being applied

to the PA to filter out-of-band noise and higher order

harmonics from the amplified signal.

Due to the varying distances between the cable modem and the

head-end, the upstream PA must be capable of varying the

output power by applying gain or attenuation. The ability to

vary the output power of the AD8328 ensures that the signal

from the cable modem has the proper level once it arrives at the

head-end. The upstream signal path commonly includes a

diplexer and cable splitters. The AD8328 has been designed to

overcome losses associated with these passive components in

the upstream cable path.

CIRCUIT DESCRIPTION

The AD8328 is composed of three analog functions in the

power-up or forward mode. The input amplifier (preamp) can

be used single-ended or differentially. If the input is used in the

differential configuration, it is imperative that the input signals

be 180° out of phase and of equal amplitude. A vernier is used

in the input stage for controlling the fine 1 dB gain steps. This

stage then drives a DAC, which provides the bulk of the

AD8328’s attenuation. The signals in the preamp and DAC gain

blocks are differential to improve the PSRR and linearity. A

differential current is fed from the DAC into the output stage.

The output stage maintains 300 Ω differential output impedance,

which maintains proper match to 75 Ω when used with a 2:1

balun transformer.

1

2

V

IN

1

2

V

IN

Figure 19. Characterization Circuit

V

V

BYP

IN+

IN–

AD8328

V

5V

CC

GND

V

V

OUT+

OUT–

Rev. A | Page 10 of 20

R

L

SPI PROGRAMMING AND GAIN ADJUSTMENT

The AD8328 is controlled through a serial peripheral interface

(SPI) of three digital data lines: CLK, DATEN , and SDATA.

Changing the gain requires eight bits of data to be streamed into

the SDATA port. The sequence of loading the SDATA register

begins on the falling edge of the DATEN pin, which activates

the CLK line. With the CLK line activated, data on the SDATA

line is clocked into the serial shift register on the rising edge of

the CLK pulses, MSB first. The 8-bit data-word is latched into

the attenuator core on the rising edge of the DATEN line. This

provides control over the changes in the output signal level. The

serial interface timing for the AD8328 is shown in Figure 3 and

Figure 4. The programmable gain range of the AD8328 is

−28 dB to +31 dB with steps of 1 dB per least significant bit

(LSB). This provides a total gain range of 59 dB. The AD8328

was characterized with a differential signal on the input and a

TOKO 458PT-1087 2:1 transformer on the output. The AD8328

incorporates supply current scaling with gain code, as shown in

Figure 18. This allows reduced power consumption when

operating in lower gain codes.

INPUT BIAS, IMPEDANCE, AND TERMINATION

The V

the input signal should be ac-coupled as shown in Figure 20.

The differential input impedance of the AD8328 is approximately

1.6 kΩ, while the single-ended input is 800 Ω. The high input

impedance of the AD8328 allows flexibility in termination and

properly matching filter networks. The AD8328 exhibits

optimum performance when driven with a pure differential

signal.

OUTPUT BIAS, IMPEDANCE, AND TERMINATION

The output stage of the AD8328 requires a bias of 5 V. The 5 V

power supply should be connected to the center tap of the

output transformer. In addition, the V

tap of the transformer should be decoupled as seen in Figure 20.

IN+

and V

IN−

inputs have a dc bias level of V

CC

applied to the center

CC

/2; therefore,