HCS240D Intersil Corporation, HCS240D Datasheet

HCS240D

Related parts for HCS240D

HCS240D Summary of contents

Page 1

... SBDIP Package (D suffix). Ordering Information PART NUMBER TEMPERATURE RANGE HCS240DMSR HCS240KMSR HCS240D/Sample HCS240K/Sample HCS240HMSR CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999 HCS240MS Octal Buffer/Line Driver, Three-State ...

Page 2

Functional Diagram AO1 AI1 H = High Voltage Level, L =Low Voltage Level X = Immaterial, Z =High Impedance HCS240MS AO2 AO3 AO4 BO1 BO2 ...

Page 3

Absolute Maximum Ratings Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to +7.0V Input Voltage ...

Page 4

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS PARAMETER SYMBOL Propagation Delay TPHL1 VCC = 4.5V, VIH = 4.5V, VIL = 0V Propagation Delay TPLH1 VCC = 4.5V, VIH = 4.5V, VIL = 0V Propagation Delay TPZL1 VCC = 4.5V, VIH = ...

Page 5

TABLE 4. POST IRRADIATION ELECTRICAL PERFORMANCE CHARACTERISTICS PARAMETER SYMBOL Supply Current ICC VCC = 5.5V, VIN = VCC or GND Output Current IOH VCC = VIH = 4.5V, VOUT = VCC -0.4V, (Source) VIL = 0 Output Current (Sink) IOL ...

Page 6

CONFORMANCE GROUPS Initial Test (Preburn-In) Interim Test I (Postburn-In) Interim Test II (Postburn-In) PDA Interim Test III (Postburn-In) PDA Final Test Group A (Note 1) Group B Subgroup B-5 Subgroup B-6 Group D NOTE: 1. Alternate group A testing in ...

Page 7

Intersil Space Level Product Flow - ‘MS’ Wafer Lot Acceptance (All Lots) Method 5007 (Includes SEM) GAMMA Radiation Verification (Each Wafer) Method 1019, 4 Samples/Wafer, 0 Rejects 100% Nondestructive Bond Pull, Method 2023 Sample - Wire Bond Pull Monitor, Method ...

Page 8

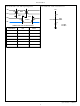

Propagation Delay Timing Diagram VIH INPUT VS VSS TPLH VOH VS OUTPUT VOL Transition Timing Diagram TTLH VOH 80% 20% OUTPUT VOL VOLTAGE LEVELS PARAMETER HCS VCC 4.50 VIH 4.50 VS 2.25 VIL 0 GND 0 Three-State High Timing Diagrams ...

Page 9

Three-State Low Timing Diagrams VIH INPUT VS VSS TPZL VOZ VT OUTPUT VOL THREE-STATE LOW VOLTAGE LEVELS PARAMETER HCS VCC 4.50 VIH 4.50 VS 2.25 VT 2.25 VW 0.90 GND 0 HCS240MS Three-State Low Load Circuit TPLZ VW UNITS V ...

Page 10

... All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification. Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use ...