MAX5942BCSE Maxim Integrated, MAX5942BCSE Datasheet - Page 13

MAX5942BCSE

Manufacturer Part Number

MAX5942BCSE

Description

Power Switch ICs - POE / LAN

Manufacturer

Maxim Integrated

Datasheet

1.MAX5942ACSE-T.pdf

(24 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MAX5942BCSE

Manufacturer:

MAXIM

Quantity:

5

Company:

Part Number:

MAX5942BCSE+

Manufacturer:

Maxim Integrated Products

Quantity:

135

Part Number:

MAX5942BCSE+

Manufacturer:

MAXIM/美信

Quantity:

20 000

Company:

Part Number:

MAX5942BCSE+T

Manufacturer:

MAXIM

Quantity:

318

The PSE determines the class of a PD by applying a volt-

age at the PD input and measures the current sourced

out of the PSE. When the PSE applies a voltage between

12.6V and 20V, the MAX5942A/MAX5942B exhibit a cur-

rent characteristic with values indicated in Table 2. The

PSE uses the classification current information to classify

the power requirement of the PD. The classification cur-

rent includes the current drawn by the 25.5kΩ detection

signature resistor and the supply current of the

MAX5942A/MAX5942B so that the total current drawn by

the PD is within the IEEE 802.3af standard figures. The

classification current is turned off whenever the device is

in power mode.

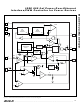

During power mode, when V

age lockout threshold (V

MAX5942B gradually turn on the internal N-channel MOS-

FET Q1 (see Figure 2). The MAX5942A/MAX5942B

charge the gate of Q1 with a constant current source

(10µA, typ). The drain-to-gate capacitance of Q1 limits

the voltage rise rate at the drain of MOSFET, thereby limit-

ing the inrush current. To reduce the inrush current, add

external drain-to-gate capacitance (see the Inrush

Current section). When the drain of Q1 is within 1.2V of its

source voltage and its gate-to-source voltage is above

5V, the MAX5942A/MAX5942B assert the PGOOD/

PGOOD outputs. The MAX5942A/MAX5942B have a wide

UVLO hysteresis and turn-off deglitch time to compensate

for the high impedance of the twisted-pair cable.

The MAX5942A/MAX5942B operate up to a 67V supply

voltage with a default UVLO turn-on set at 39V and a

UVLO turn-off set at 30V. Adjust the UVLO threshold

using a resistor-divider connected to UVLO (see Figure

3). When the input voltage is above the UVLO threshold

(V

on. When the input voltage goes below the UVLO thresh-

old (V

turns off.

To adjust the UVLO threshold, connect an external

resistor-divider from GND to UVLO and from UVLO to

V

R2 for a desired UVLO threshold:

where V

resistor-divider replaces the 25.5kΩ PD detection resis-

tor, ensure that the sum of R1 and R2 equals 25.5kΩ

EE

UVLO,ON

. Use the following equations to calculate R1 and

UVLO,OFF

IN,EX

), the IC is in power mode and the MOSFET is

Interface/PWM Controller for Power Devices

is the desired UVLO threshold. Since the

R

) for more than t

2

=

______________________________________________________________________________________

R1 = 25.5kΩ - R2

25 5

.

k

Ω

Undervoltage Lockout

UVLO,ON

IN

x

rises above the undervolt-

V

REF UVLO

OFF_DLY

V

INEX

IEEE 802.3af Power-Over-Ethernet

,

,

), the MAX5942A/

, the MOSFET

Power Mode

±1%. When using the external resistor-divider, the

MAX5942 has an external reference voltage hysteresis of

20% (typ). In other words, when UVLO is programmed

externally, the turn-off threshold will be 80% (typ) of the

new UVLO turn-on threshold.

The MAX5942A/MAX5942B charge the gate of the inter-

nal MOSFET with a constant current source (10µA, typ).

The drain-to-gate capacitance of the MOSFET limits the

voltage rise rate at the drain, thereby limiting the inrush

current. Add an external capacitor from GATE to OUT

to further reduce the inrush current. Use the following

equation to calculate the inrush current:

The recommended inrush current for a PoE application

is 100mA.

PGOOD is an open-drain, active-high logic output.

PGOOD goes high impedance when V

of V

PGOOD is pulled to V

below GND). Connect PGOOD to SS_SHDN to enable

the PWM controller.

PGOOD is an open-drain, active-low logic output.

PGOOD is pulled to V

and when GATE is 5V above V

goes high impedance.

Figure 3. Setting Undervoltage Lockout with an External

Resistor-Divider

EE

and when GATE is 5V above V

V

IN

= 24V TO 60V

I

R2

INRUSH

R1

EE

OUT

when V

=

PGOOD/

UVLO

(given that V

I x

G

Inrush Current Limit

MAX5942A

MAX5942B

OUT

C

C

EE

GND

GATE

V

OUT

EE

. Otherwise, PGOOD

PGOOD Outputs

is within 1.2V of V

OUT

OUT

EE

is within 1.2V

. Otherwise,

is at least 5V

13

EE