AD5259EVAL Analog Devices Inc, AD5259EVAL Datasheet - Page 19

AD5259EVAL

Manufacturer Part Number

AD5259EVAL

Description

BOARD EVAL FOR AD5259 DGTL POT

Manufacturer

Analog Devices Inc

Datasheet

1.AD5259BRMZ10.pdf

(24 pages)

Specifications of AD5259EVAL

Main Purpose

Digital Potentiometer

Utilized Ic / Part

AD5259

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Secondary Attributes

-

Embedded

-

Primary Attributes

-

Lead Free Status / Rohs Status

Not Compliant

ESD PROTECTION OF DIGITAL PINS AND

RESISTOR TERMINALS

The AD5259 V

boundary conditions for proper 3-terminal and digital input

operation. Supply signals present on Terminal A, Terminal B,

and Terminal W that exceed V

internal forward biased ESD protection diodes (see Figure 42).

Digital Input SCL and Digital Input SDA are clamped by ESD

protection diodes with respect to V

Figure 43.

POWER-UP SEQUENCE

Because the ESD protection diodes limit the voltage compliance

at Terminal A, Terminal B, and Terminal W (see Figure 42), it

is important to power GND/V

voltage to Terminal A, Terminal B, and Terminal W; otherwise,

the diode is forward biased, so the V

unintentionally and may affect the user’s circuit. The ideal power-

up sequence is in the following order: GND, V

inputs, and then V

V

they are powered after GND/V

A

, V

B

, V

Figure 43. Maximum Terminal Voltages Set by V

Figure 42. Maximum Terminal Voltages Set by V

W

, and the digital inputs is not important as long as

DD

, V

A

, V

LOGIC

B

, V

, and GND power supplies define the

W

. The relative order of powering

DD

DD

DD

/V

/V

or GND are clamped by the

LOGIC

LOGIC

DD

LOGIC

and V

and GND as shown in

before applying any

.

V

A

W

B

GND

V

SCL

SDA

GND

DD

LOGIC

LOGIC

DD

LOGIC

DD

, V

are powered

and GND

and GND

LOGIC

, digital

Rev. B | Page 19 of 24

LAYOUT AND POWER SUPPLY BYPASSING

It is good practice to use compact, minimum lead length layout

design. The leads to the inputs should be as direct as possible

with minimum conductor length. Ground paths should have

low resistance and low inductance.

Similarly, it is also good practice to bypass the power supplies

with quality capacitors for optimum stability. Supply leads to

the device should be bypassed with disc or chip ceramic capaci-

tors of 0.01 μF to 0.1 μF. Low ESR 1 μF to 10 μF tantalum or

electrolytic capacitors should also be applied at the supplies to

minimize any transient disturbance and low frequency ripple

(see Figure 44). The digital ground should also be joined

remotely to the analog ground at one point to minimize the

ground bounce.

MULTIPLE DEVICES ON ONE BUS

The AD5259 has two configurable address pins, Pin AD0 and

Pin AD1. The state of these two pins is registered upon power-

up and decoded into a corresponding I

address (see Table 5). This allows up to four devices on the bus

to be written to or read from independently.

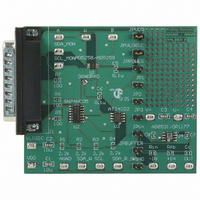

EVALUATION BOARD

An evaluation board, with all necessary software, is available

to program the AD5259 from any PC running Windows® 98/

2000/ XP. The graphical user interface, as shown in Figure 45,

is straightforward and easy to use. More detailed information

is available in the board’s user manual.

V

Figure 45. AD5259 Evaluation Board Software

DD

10F

Figure 44. Power Supply Bypassing

C2

+

0.1F

C1

V

DD

AD5259

2

C-compatible 7-bit

GND

AD5259