DM164120-1 Microchip Technology, DM164120-1 Datasheet - Page 33

DM164120-1

Manufacturer Part Number

DM164120-1

Description

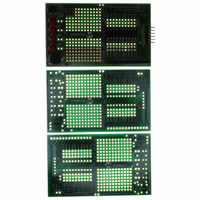

BOARD DEMO PICKIT 2 LP COUNT

Manufacturer

Microchip Technology

Type

MCUr

Datasheet

1.DM164120-1.pdf

(42 pages)

Specifications of DM164120-1

Contents

3 Boards (1 Populated, 2 Bare)

Processor To Be Evaluated

PIC16F690

Silicon Manufacturer

Microchip

Core Architecture

PIC

Core Sub-architecture

PIC16

Silicon Core Number

PIC16F

Silicon Family Name

PIC16F6xxx

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

28-pin PIC16C, 16F, 18C, 18F

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DM164120-1

Manufacturer:

Microchip Technology

Quantity:

135

© 2005 Microchip Technology Inc.

3.2.10

New Instructions

Interrupt Sources

Most of the peripherals can generate an interrupt; also some of the I/O pins may be

configured to generate an interrupt when they change state.

When a peripheral needs service, it sets its interrupt flag. Each interrupt flag is ANDed

with its enable bit and then these are ORed together to form a Master Interrupt. This

master interrupt is ANDed with the Global Interrupt Enable (GIE). See the Interrupt

Logic Figure in the PIC16F685/687/689/690 Data Sheet (DS41262) for a complete

drawing of the interrupt logic. The enable bits allow the PICmicro to limit the interrupt

sources to certain peripherals.

FIGURE 3-9:

When the master interrupt line is asserted, the PICmicro finishes the current

instruction, stores the next address on the CALL stack then jumps to the Interrupt

Service Routine (ISR). It also clears the GIE bit, preventing another interrupt from

occurring while servicing the current one.

Save Current Context

The first thing the ISR must do is to save the current context of the processor so it can

be restored before returning to the main program. Any SFR that may be changed in the

ISR must be saved, which means the Wreg and Status registers at the very least. The

last 16 bytes of each PIC16F690 file register page are unbanked and are good places

to save the context, as they may be accessed from any register page without regard to

the RP0 and RP1 bits in the Status register. The location of unbanked registers may

vary from part to part. Check the register map to find the unbanked region for a specific

part.

Identify Triggering Event

Next, the ISR has to figure out what triggered the interrupt. It has to check the interrupt

flags to determine what caused the interrupt. When it finds the source, then it can

service the peripheral.

Interrupt Flag

Interrupt Enable

RETFIE

SWAPF

Lesson 10: Interrupts

Other Interrupt Sources

INTERRUPT LOGIC SIMPLIFIED

Return from Interrupt

Swap nibbles in file register

LPC Demo Board Lessons

Global Interrupt Enable

Master Interrupt

DS51556A-page 29