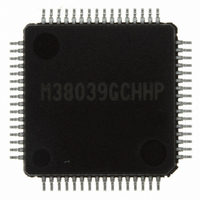

M38039GCHHP#U0 Renesas Electronics America, M38039GCHHP#U0 Datasheet - Page 72

M38039GCHHP#U0

Manufacturer Part Number

M38039GCHHP#U0

Description

IC 740/3803 MCU QZROM 64LQFP

Manufacturer

Renesas Electronics America

Series

740/38000r

Datasheet

1.M38039G4HHPU0.pdf

(105 pages)

Specifications of M38039GCHHP#U0

Core Processor

740

Core Size

8-Bit

Speed

16.8MHz

Connectivity

SIO, UART/USART

Peripherals

LED, PWM, WDT

Number Of I /o

56

Program Memory Size

48KB (48K x 8)

Program Memory Type

QzROM

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

64-LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

3803 Group (Spec.H QzROM version)

REJ03B0166-0113 Rev.1.13

Page 70 of 100

Fig 66. System clock generating circuit block diagram (Single-chip mode)

Interrupt disable flag l

Notes1: Either high-speed, middle-speed or low-speed mode is selected by bits 7 and 6 of the CPU mode register.

Interrupt request

2: f(X

3: When bit 0 of MISRG is “0”, timer 1 is set “01

4: Although a feed-back resistor exists on-chip, an external feed-back resistor may be needed depending on conditions.

X

When low-speed mode is selected, set port X

supplied as the count source at executing STP instruction.

appropriate value to them in accordance with oscillation stabilizing time required by the using oscillator because nothing is

automatically set into timer 1 and prescaler 12.

CIN

IN

X

)/16 is supplied as the count source to the prescaler 12 at reset, the count source before executing the STP instruction is

IN

Q

(Note 4)

S

R

“1”

Reset

X

COUT

X

STP

instruction

OUT

“0”

Port X

switch bit

Main clock (X

High-speed or

middle-speed mode

Main clock division ratio

selection bits (Note 1)

Low-speed

mode

C

Aug 21, 2009

IN

-X

OUT

) stop bit

instruction

1/2

16

C

” and prescaler 12 is set “FF

switch bit (b4) to “1”.

High-speed or

low-speed mode

WIT

1/4

S

R

Divider

Main clock division ratio

selection bits (Note 1)

Q

Middle-speed mode

16

” automatically. When bit 0 of MISRG is “1” , set the

Q

S

R

Prescaler 12

STP

instruction

Timing φ (internal clock)

(Note 3)

Timer 1

Reset or

STP instruction

(Note 2)

Reset