A3P015-QNG68 Actel, A3P015-QNG68 Datasheet - Page 104

A3P015-QNG68

Manufacturer Part Number

A3P015-QNG68

Description

FPGA - Field Programmable Gate Array 15K System Gates

Manufacturer

Actel

Datasheet

1.A3P1000-FGG144.pdf

(218 pages)

Specifications of A3P015-QNG68

Processor Series

A3P015

Core

IP Core

Number Of Macrocells

128

Maximum Operating Frequency

350 MHz

Number Of Programmable I/os

49

Supply Voltage (max)

3.3 V

Supply Current

2 mA

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Development Tools By Supplier

A3PE-Proto-Kit, A3PE-Brd1500-Skt, Silicon-Explorer II, Silicon-Sculptor 3, SI-EX-TCA, FlashPro 4, FlashPro 3, FlashPro Lite

Mounting Style

SMD/SMT

Supply Voltage (min)

1.5 V

Number Of Gates

15 K

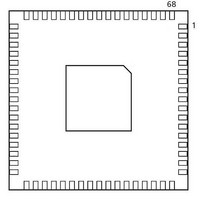

Package / Case

QFN-68

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

A3P015-QNG68

Manufacturer:

ACTEL

Quantity:

954

Company:

Part Number:

A3P015-QNG68PS32

Manufacturer:

VIS

Quantity:

2 722

- Current page: 104 of 218

- Download datasheet (7Mb)

ProASIC3 DC and Switching Characteristics

Table 2-111 • A3P250 Global Resource

Table 2-112 • A3P400 Global Resource

2- 90

Parameter

t

t

t

t

t

F

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element,

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully

3. For specific junction temperature and voltage supply levels, refer to

Parameter

t

t

t

t

t

F

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element,

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully

3. For specific junction temperature and voltage supply levels, refer to

RCKL

RCKH

RCKMPWH

RCKMPWL

RCKSW

RCKL

RCKH

RCKMPWH

RCKMPWL

RCKSW

RMAX

RMAX

located in a lightly loaded row (single element is connected to the global net).

loaded row (all available flip-flops are connected to the global net in the row).

located in a lightly loaded row (single element is connected to the global net).

loaded row (all available flip-flops are connected to the global net in the row).

Commercial-Case Conditions: T

Commercial-Case Conditions: T

Input Low Delay for Global Clock

Input High Delay for Global Clock

Minimum Pulse Width High for Global Clock

Minimum Pulse Width Low for Global Clock

Maximum Skew for Global Clock

Maximum Frequency for Global Clock

Input Low Delay for Global Clock

Input High Delay for Global Clock

Minimum Pulse Width High for Global Clock

Minimum Pulse Width Low for Global Clock

Maximum Skew for Global Clock

Maximum Frequency for Global Clock

Description

Description

J

J

= 70°C, VCC = 1.425 V

= 70°C, VCC = 1.425 V

R e visio n 9

Min.

Min.

0.80

0.78

Table 2-6 on page 2-6

Table 2-6 on page 2-6

0.87

0.86

1

1

–2

–2

Max.

Max.

1.01

1.04

0.26

1.09

1.11

0.26

2

2

Min.

Min.

0.91

0.89

0.99

0.98

1

1

–1

–1

Max.

for derating values.

Max.

for derating values.

1.15

1.18

0.29

1.24

1.27

0.29

2

2

Min.

Min.

1.07

1.04

1.17

1.15

Std.

1

Std.

1

Max.

Max.

1.36

1.39

0.34

1.46

1.49

0.34

2

2

Units

Units

MHz

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Related parts for A3P015-QNG68

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

ProASIC3 Flash Family FPGAs

Manufacturer:

ACTEL [Actel Corporation]

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Silicon Sculptor Programming Mod

Manufacturer:

Actel

Part Number:

Description:

MCU, MPU & DSP Development Tools InSystem Programming ProASICPLUS Devices

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators PQ160 Module

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators AFDX Solutions

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators SILICON SCULPTOR ADAPTER MODULE

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Silicon Sculptor Software

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators InSystem Programming ProASICPLUS Devices

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel