A3P015-QNG68 Actel, A3P015-QNG68 Datasheet - Page 24

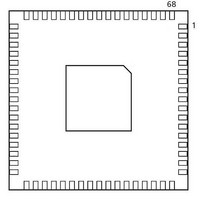

A3P015-QNG68

Manufacturer Part Number

A3P015-QNG68

Description

FPGA - Field Programmable Gate Array 15K System Gates

Manufacturer

Actel

Datasheet

1.A3P1000-FGG144.pdf

(218 pages)

Specifications of A3P015-QNG68

Processor Series

A3P015

Core

IP Core

Number Of Macrocells

128

Maximum Operating Frequency

350 MHz

Number Of Programmable I/os

49

Supply Voltage (max)

3.3 V

Supply Current

2 mA

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Development Tools By Supplier

A3PE-Proto-Kit, A3PE-Brd1500-Skt, Silicon-Explorer II, Silicon-Sculptor 3, SI-EX-TCA, FlashPro 4, FlashPro 3, FlashPro Lite

Mounting Style

SMD/SMT

Supply Voltage (min)

1.5 V

Number Of Gates

15 K

Package / Case

QFN-68

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

A3P015-QNG68

Manufacturer:

ACTEL

Quantity:

954

Company:

Part Number:

A3P015-QNG68PS32

Manufacturer:

VIS

Quantity:

2 722

- Current page: 24 of 218

- Download datasheet (7Mb)

ProASIC3 DC and Switching Characteristics

Table 2-14 • Different Components Contributing to Dynamic Power Consumption in ProASIC3 Devices

2- 10

Parameter

P

P

P

P

P

P

P

P

P

P

P

P

P

Note:

AC1

AC2

AC3

AC4

AC5

AC6

AC7

AC8

AC9

AC10

AC11

AC12

AC13

*For a different output load, drive strength, or slew rate, Actel recommends using the Actel Power spreadsheet

calculator or SmartPower tool in Libero

Power Consumption of Various Internal Resources

Clock contribution of a Global Rib

Clock contribution of a Global Spine

Clock contribution of a VersaTile row

Clock contribution of a VersaTile used as a

sequential module

First contribution of a VersaTile used as a

sequential module

Second contribution of a VersaTile used as a

sequential module

Contribution of a VersaTile used as a

combinatorial Module

Average contribution of a routing net

Contribution of an I/O input pin (standard

dependent)

Contribution of an I/O output pin (standard

dependent)

Average contribution of a RAM block during a

read operation

Average contribution of a RAM block during a

write operation

Dynamic contribution for PLL

Definition

®

Integrated Design Environment (IDE) software.

R e visio n 9

14.50 12.80 12.80 11.00 11.00 9.30 9.30 9.30

2.48

Device Specific Dynamic Contributions

1.85

See

See

Table 2-11 on page 2-8

Table 2-8 on page 2-6

1.35

Table 2-10 on page

Table 2-13 on page

(µW/MHz)

1.58

25.00

30.00

0.81

0.70

2.60

0.12

0.07

0.29

0.29

0.81

2-7.

2-9.

0.81 0.41 0.41

through

through

Related parts for A3P015-QNG68

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

ProASIC3 Flash Family FPGAs

Manufacturer:

ACTEL [Actel Corporation]

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Silicon Sculptor Programming Mod

Manufacturer:

Actel

Part Number:

Description:

MCU, MPU & DSP Development Tools InSystem Programming ProASICPLUS Devices

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators PQ160 Module

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators AFDX Solutions

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators SILICON SCULPTOR ADAPTER MODULE

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Silicon Sculptor Software

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators InSystem Programming ProASICPLUS Devices

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel