AD2S90APZ Analog Devices Inc, AD2S90APZ Datasheet

AD2S90APZ

Specifications of AD2S90APZ

Available stocks

Related parts for AD2S90APZ

AD2S90APZ Summary of contents

Page 1

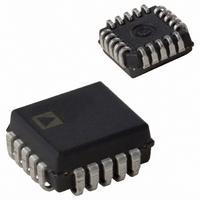

FEATURES Complete Monolithic Resolver-to-Digital Converter Incremental Encoder Emulation (1024-Line) Absolute Serial Data (12-Bit) Differential Inputs 12-Bit Resolution Industrial Temperature Range 20-Lead PLCC Low Power (50 mW) APPLICATIONS Industrial Motor Control Servo Motor Control Industrial Gauging Encoder Emulation Automotive Motion ...

Page 2

AD2S90–SPECIFICATIONS Parameter SIGNAL INPUTS Voltage Amplitude Frequency Input Bias Current Input Impedance 1 Common-Mode Volts CMRR REFERENCE INPUT Voltage Amplitude Frequency Input Bias Current Input Impedance Permissible Phase Shift CONVERTER DYNAMICS Bandwidth Maximum Tracking Rate Maximum VCO Rate (CLKOUT) Settling ...

Page 3

TIMING CHARACTERISTICS CSB SCLK DATA NOTES 1 Timing data are not 100% production tested. Sample tested at +25 C only to ensure conformance to data sheet limits. Logic output timing tests carried out using 10 pF, 100 k load. 2 ...

Page 4

AD2S90 RECOMMENDED OPERATING CONDITIONS Power Supply Voltage (V – Analog Input Voltage (SIN, COS & REF rms Signal and ...

Page 5

RESOLVER FORMAT SIGNALS A resolver is a rotating transformer which has two stator wind- ings and one rotor winding. The stator windings are displaced mechanically by 90 (see Figure 4). The rotor is excited with an ac reference. The amplitude ...

Page 6

AD2S90 ABSOLUTE POSITION OUTPUT SERIAL INTERFACE Absolute angular position is represented by serial binary data and is extracted via a three-wire interface, DATA, CS and SCLK. The DATA output is held in a high impedance state when CS is HI. ...

Page 7

VELOCITY OUTPUT The analog velocity output VEL is scaled to produce 150 rps/V dc 15%. The sense is positive V dc for increasing angular rotation. VEL can drive a maximum load combination and 30 pF. The internal ...

Page 8

AD2S90 TMS32020 Interfacing Figure 11 shows the serial interface between the AD2S90 and the TMS32020. The interface is configured in alternate internal framing, external clock (externally inverted) mode. Sixteen bits of data are clocked from the AD2S90 into the data ...

Page 9

REMOTE MULTIPLE SENSOR INTERFACING The DATA output of the AD2S90 is held in a high impedance state until CS is taken LO. This allows a user to operate the AD2S90 in an application with more than one converter con- nected ...

Page 10

AD2S90 The small step response is given in Figure 20, and is the time taken for the converter to settle to within 1 LSB 7.00 ms (maximum) The large step response (steps >20 ) applies when the error ...

Page 11

AD2S90/AD2S99 TYPICAL CONFIGURATION Figure 21 shows a typical circuit configuration for the AD2S99 Oscillator and the AD2S90 Resolver-to-Digital Converter. The maximum level of the SIN and COS input signals to the AD2S90 should rms 10%. All the ...

Page 12

AD2S90 0.048 (1.21) 0.042 (1.07) OUTLINE DIMENSIONS Dimensions shown in inches and (mm). P-20A 20-Lead Plastic Leaded Chip Carrier (PLCC) 0.180 (4.57) 0.165 (4.19) 0.048 (1.21) 0.056 (1.42) 0.042 (1.07) 0.025 (0.63) 0.042 (1.07) 0.015 (0.38 0.021 (0.53) ...