XC3S1600E-5FG320C Xilinx Inc, XC3S1600E-5FG320C Datasheet - Page 92

XC3S1600E-5FG320C

Manufacturer Part Number

XC3S1600E-5FG320C

Description

PROGRAMMABLE MICROCHIP

Manufacturer

Xilinx Inc

Datasheet

1.XC3S1600E-5FG320C.pdf

(193 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 92 of 193

- Download datasheet (2Mb)

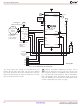

Table 56: Slave Serial Mode Connections

Voltage Compatibility

FPGA’s I/O Bank 2, supplied by the VCCO_2 supply input.

The VCCO_2 voltage can be 3.3V, 2.5V, or 1.8V to match

the requirements of the external host, ideally 2.5V. Using

3.3V or 1.8V requires additional design considerations as

the DONE and PROG_B pins are powered by the FPGA’s

2.5V VCCAUX supply. See application note XAPP453: "The

3.3V Configuration of Spartan-3 FPGAs" for additional infor-

mation.

DS312-2 (v1.1) March 21, 2005

Advance Product Specification

HSWAP

M[2:0]

DIN

CCLK

INIT_B

DONE

PROG_B

V

Pin Name

Most Slave Serial interface signals are within the

R

FPGA Direction

bidirectional I/O

bidirectional I/O

Open-drain

Open-drain

Input

Input

Input

Input

Input

User I/O Pull-Up Control. When

Low during configuration, enables

pull-up resistors in all I/O pins to

respective I/O bank

0: Pull-up during configuration

1: No pull-ups

Mode Select. Selects the FPGA

configuration mode.

Data Input.

Configuration Clock. If CCLK

PCB trace is long or has multiple

connections, terminate this output

to maintain signal integrity.

Initialization Indicator. Active

Low. Goes Low at start of

configuration during Initialization

memory clearing process.

Released at end of memory

clearing, when mode select pins

are sampled. In daisy-chain

applications, this signal requires

an external 4.7 kΩ pull-up resistor

to VCCO_2.

FPGA Configuration Done. Low

during configuration. Goes High

when FPGA successfully

completes configuration.

Requires external 330 Ω pull-up

resistor to 2.5V.

Program FPGA. Active Low.

When asserted Low for 300 ns or

longer, forces the FPGA to restart

its configuration process by

clearing configuration memory

and resetting the DONE and

INIT_B pins once PROG_B

returns High. Requires external

4.7 kΩ pull-up resistor to 2.5V. If

driving externally, use an

open-drain or open-collector

driver.

Description

V

CCO

www.xilinx.com

input.

Daisy-Chaining

If the application requires multiple FPGAs with different con-

figurations, then configure the FPGAs using a daisy chain,

as

(M[2:0] = <1:1:1>) for all FPGAs in the daisy-chain. After

the lead FPGA is filled with its configuration data, the lead

FPGA passes configuration data via its DOUT output pin to

the next FPGA on the falling CCLK edge.

Drive at valid logic level

throughout configuration.

M2 = 1, M1 = 1, M0 = 1 Sampled

when INIT_B goes High.

Serial data provided by host.

FPGA captures data on rising

CCLK edge.

External clock.

Active during configuration. If

CRC error detected during

configuration, FPGA drives

INIT_B Low.

Low indicates that the FPGA is

not yet configured.

Must be High to allow

configuration to start.

shown

During Configuration

in

Figure

61.

Use

User I/O

User I/O

User I/O

User I/O

User I/O

Pulled High via external

pull-up. When High,

indicates that the FPGA

successfully configured.

Drive PROG_B Low and

release to reprogram

FPGA.

Functional Description

After Configuration

Slave

Serial

mode

85

Related parts for XC3S1600E-5FG320C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC SPARTAN-3E FPGA 1600K 320-FBG

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC SPARTAN-3E FPGA 1600K 400FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA SPARTAN-3E 1600K 320FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA SPARTAN-3E 1600K 320FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA SPARTAN-3E 1600K 400FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA SPARTAN-3E 1600K 484FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA SPARTAN 3E 320FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA SPARTAN 3E 400FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA SPARTAN 3E 484FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

FPGA, SPARTAN-3E, 1600K GATES, 484FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

FPGA Spartan®-3E Family 1.6M Gates 33192 Cells 572MHz 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

FPGA Spartan®-3E Family 1.6M Gates 33192 Cells 657MHz 90nm (CMOS) Technology 1.2V 400-Pin FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

FPGA Spartan®-3E Family 1.6M Gates 33192 Cells 657MHz 90nm (CMOS) Technology 1.2V 400-Pin FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

FPGA Spartan®-3E Family 1.6M Gates 33192 Cells 572MHz 90nm (CMOS) Technology 1.2V 320-Pin FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC CPLD .8K 36MCELL 44-VQFP

Manufacturer:

Xilinx Inc

Datasheet: