IDT5T9304PGGI8 IDT, Integrated Device Technology Inc, IDT5T9304PGGI8 Datasheet - Page 7

IDT5T9304PGGI8

Manufacturer Part Number

IDT5T9304PGGI8

Description

IC CLK BUFFER 1:4 LVDS 24-TSSOP

Manufacturer

IDT, Integrated Device Technology Inc

Series

TERABUFFER™ IIr

Type

Fanout Buffer (Distribution), Multiplexerr

Datasheet

1.IDT5T9304PGGI8.pdf

(15 pages)

Specifications of IDT5T9304PGGI8

Number Of Circuits

1

Ratio - Input:output

2:4

Differential - Input:output

Yes/Yes

Input

CML, eHSTL, HSTL, LVDS, LVEPECL, LVPECL, LVTTL

Output

LVDS

Frequency - Max

450MHz

Voltage - Supply

2.3 V ~ 2.7 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

24-TSSOP

Frequency-max

450MHz

Number Of Clock Inputs

2

Mode Of Operation

Differential

Output Frequency

450MHz

Output Logic Level

LVDS

Operating Supply Voltage (min)

2.3V

Operating Supply Voltage (typ)

2.5V

Operating Supply Voltage (max)

2.7V

Package Type

TSSOP

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

24

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

5T9304PGGI8

Table 5B. eHSTL AC Differential Input Characteristics, T

NOTE 1. The 1V peak-to-peak input pulse level is specified to allow consistent, repeatable results in an automatic test equipment (ATE)

environment. This device meets the V

NOTE 2. A 900mV crossing point level is specified to allow consistent, repeatable results in an automatic test equipment (ATE)

environment. This device meets the V

NOTE 3. In all cases, input waveform timing is marked at the differential cross-point of the input signals.

NOTE 4. The input signal edge rate of 2V/ns or greater is to be maintained in the 20% to 80% range of the input waveform.

Table 5C. LVEPECL (2.5V) and LVPECL (3.3V) Differential Input AC Characteristics, T

NOTE 1. The 732mV peak-to-peak input pulse level is specified to allow consistent, repeatable results in an automatic test equipment

(ATE) environment. This device meets the V

NOTE 2. A 1082mV LVEPECL (2.5V) and 1880 LVPECL (3.3V) crossing point level is specified to allow consistent, repeatable results in

an automatic test equipment (ATE) environment. This device meets the V

NOTE 3. In all cases, input waveform timing is marked at the differential cross-point of the input signals.

N

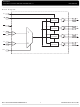

IIDT™ LVDS CLOCK BUFFER TERABUFFER™ II

Symbol

V

V

D

V

t

Symbol

V

V

D

V

t

OTE 4. The input signal edge rate of 2V/ns or greater is to be maintained in the 20% to 80% range of the input waveform.

R

R

IDT5T9304

2.5V LVDS 1:4 CLOCK BUFFER TERABUFFER™ II

DIF

X

THI

DIF

X

THI

H

H

/ t

/ t

F

F

Parameter

Input Signal Swing

Differential Input Signal Crossing Point

Duty Cycle

Input Timing Measurement Reference Level

Input Signal Edge Rate

Parameter

Input Signal Swing

Differential Input Cross Point Voltage

Duty Cycle

Input Timing Measurement Reference Level

Input Signal Edge Rate

(1)

(1)

(4)

DIF

X

(4)

specification under actual use conditions.

(AC) specification under actual use conditions.

DIF

(AC) specification under actual use conditions.

(2)

(2)

(3)

(3)

LVEPECL

LVPECL

A

7

= -40°C to 85°C

X

specification under actual use conditions.

A

= -40°C to 85°C

Crossing Point

IDT5T9304 REV. A JULY 23, 2007

Crossing Point

Maximum

Value

900

50

1082

1880

1

2

732

50

2

PRELIMINARY

Units

Units

V/ns

V/ns

mV

mV

mV

mV

%

V

V

%

V