CY37064VP44-100AXC Cypress Semiconductor Corp, CY37064VP44-100AXC Datasheet - Page 17

CY37064VP44-100AXC

Manufacturer Part Number

CY37064VP44-100AXC

Description

IC CPLD 64 MACROCELL 44LQFP

Manufacturer

Cypress Semiconductor Corp

Series

Ultra37000™r

Specifications of CY37064VP44-100AXC

Programmable Type

In-System Reprogrammable™ (ISR™) Flash

Delay Time Tpd(1) Max

12.0ns

Voltage Supply - Internal

3 V ~ 3.6 V

Number Of Macrocells

64

Number Of I /o

37

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

44-LQFP

Voltage

3.3V

Memory Type

CMOS

Family Name

Ultra37000

# Macrocells

64

Number Of Usable Gates

2000

Frequency (max)

100MHz

Propagation Delay Time

12ns

Number Of Logic Blocks/elements

4

# I/os (max)

37

Operating Supply Voltage (typ)

3.3V

In System Programmable

Yes

Operating Supply Voltage (min)

3V

Operating Supply Voltage (max)

3.6V

Operating Temp Range

0C to 70C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

44

Package Type

TQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Number Of Logic Elements/cells

-

Lead Free Status / Rohs Status

Compliant

Other names

428-1937

CY37064VP44-100AXC

CY37064VP44-100AXC

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY37064VP44-100AXC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY37064VP44-100AXC

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY37064VP44-100AXCT

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY37064VP44-100AXCT

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Document #: 38-03007 Rev. *E

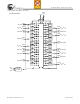

Switching Characteristics

Combinatorial Mode Parameters

t

t

t

t

t

Input Register Parameters

t

t

t

t

t

t

Synchronous Clocking Parameters

t

t

t

t

t

t

t

Notes:

11. t

12. All AC parameters are measured with two outputs switching and 35-pF AC Test Load.

13. Logic Blocks operating in Low-Power Mode, add t

14. Outputs using Slow Output Slew Rate, add t

15. When V

PD

PDL

PDLL

EA

ER

WL

WH

IS

IH

ICO

ICOL

CO

S

H

CO2

SCS

SL

HL

[13]

[13]

[13, 14, 15]

[13, 14, 15]

[11, 13]

[14, 15]

ER

[13, 14, 15]

[13, 14, 15]

[13, 14, 15]

[13]

Parameter

[13, 14, 15]

[13, 14, 15]

Parameter

measured with 5-pF AC Test Load and t

CCO

t

t

t

t

ER(–)

ER(+)

EA(+)

EA(–)

= 3.3V, add t

[11]

Input to Combinatorial Output

Input to Output Through Transparent Input or Output Latch

Input to Output Through Transparent Input and Output Latches

Input to Output Enable

Input to Output Disable

Clock or Latch Enable Input LOW Time

Clock or Latch Enable Input HIGH Time

Input Register or Latch Set-up Time

Input Register or Latch Hold Time

Input Register Clock or Latch Enable to Combinatorial Output

Input Register Clock or Latch Enable to Output Through Transparent Output Latch

Synchronous Clock (CLK

Set-Up Time from Input to Sync. Clk (CLK

Register or Latch Data Hold Time

Output Synchronous Clock (CLK

Delay (Through Logic Array)

Output Synchronous Clock (CLK

Clock (CLK

Set-Up Time from Input Through Transparent Latch to Output Register Synchronous Clock (CLK

CLK

Hold Time for Input Through Transparent Latch from Output Register Synchronous Clock (CLK

CLK

3.3IO

1

1

to this spec.

, CLK

, CLK

2

2

0

, or CLK

, or CLK

, CLK

Over the Operating Range

EA

SLEW

1.5V

2.6V

1.5V

V

measured with 35-pF AC Test Load.

1

V

, CLK

the

X

LP

3

3

to this spec.

) or Latch Enable

) or Latch Enable

to this spec.

2

0

, or CLK

, CLK

(d) Test Waveforms

1

0

0

, CLK

, CLK

, CLK

3

) or Latch Enable (Through Logic Array)

V

V

V

V

2

1

[8]

1

OH

OL

X

[8]

, or CLK

[12]

, CLK

X

, CLK

0

Description

0.5V

0.5V

0.5V

, CLK

0.5V

2

2

, or CLK

, or CLK

3

1

) or Latch Enable to Output

Output Waveform—Measurement Level

, CLK

3

3

2

) or Latch Enable to Combinatorial Output

) or Latch Enable to Output Synchronous

, or CLK

Ultra37000 CPLD Family

3

) or Latch Enable

V

V

V

V

OL

X

X

OH

Page 17 of 64

0

,

0

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns