CY37128P160-125AC Cypress Semiconductor Corp, CY37128P160-125AC Datasheet - Page 18

CY37128P160-125AC

Manufacturer Part Number

CY37128P160-125AC

Description

IC CPLD 128 MACROCELL 160LQFP

Manufacturer

Cypress Semiconductor Corp

Series

Ultra37000™r

Datasheet

1.CY37064P44-125JXC.pdf

(64 pages)

Specifications of CY37128P160-125AC

Programmable Type

In-System Reprogrammable™ (ISR™) CMOS

Delay Time Tpd(1) Max

10.0ns

Voltage Supply - Internal

4.75 V ~ 5.25 V

Number Of Macrocells

128

Number Of I /o

133

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

160-LQFP

Voltage

5V

Memory Type

CMOS

For Use With

CY3710 - ADAPTER SOCKET PTG

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Number Of Logic Elements/cells

-

Other names

428-1290

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY37128P160-125AC

Manufacturer:

CYPRESS

Quantity:

126

Company:

Part Number:

CY37128P160-125AC

Manufacturer:

CYP

Quantity:

5 510

Company:

Part Number:

CY37128P160-125AC

Manufacturer:

CYPRESS

Quantity:

217

Company:

Part Number:

CY37128P160-125AC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY37128P160-125AC

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Document #: 38-03007 Rev. *E

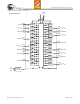

Switching Characteristics

Product Term Clocking Parameters

t

t

t

t

t

t

Pipelined Mode Parameters

t

Operating Frequency Parameters

f

f

f

f

Reset/Preset Parameters

t

t

t

t

t

t

User Option Parameters

t

t

t

t

t

t

f

COPT

SPT

HPT

ISPT

IHPT

CO2PT

ICS

MAX1

MAX2

MAX3

MAX4

RW

RR

RO

PW

PR

PO

LP

SLEW

3.3IO

S JTAG

H JTAG

CO JTAG

JTAG

JTAG Timing Parameters

[13]

[13]

[13, 14, 15]

[13, 14, 15]

[13]

[13]

Parameter

[13, 14, 15]

[13, 14, 15]

Product Term Clock or Latch Enable (PTCLK) to Output

Set-Up Time from Input to Product Term Clock or Latch Enable (PTCLK)

Register or Latch Data Hold Time

Set-Up Time for Buried Register used as an Input Register from Input to Product Term Clock or

Latch Enable (PTCLK)

Buried Register Used as an Input Register or Latch Data Hold Time

Product Term Clock or Latch Enable (PTCLK) to Output Delay (Through Logic Array)

Input Register Synchronous Clock (CLK

Clock (CLK

Maximum Frequency with Internal Feedback (Lesser of 1/t

Maximum Frequency Data Path in Output Registered/Latched Mode (Lesser of 1/(t

1/(t

Maximum Frequency with External Feedback (Lesser of 1/(t

Maximum Frequency in Pipelined Mode (Lesser of 1/(t

or 1/t

Asynchronous Reset Width

Asynchronous Reset Recovery Time

Asynchronous Reset to Output

Asynchronous Preset Width

Asynchronous Preset Recovery Time

Asynchronous Preset to Output

Low Power Adder

Slow Output Slew Rate Adder

3.3V I/O Mode Timing Adder

Set-up Time from TDI and TMS to TCK

Hold Time on TDI and TMS

Falling Edge of TCK to TDO

Maximum JTAG Tap Controller Frequency

S

+ t

SCS

H

), or 1/t

)

[5]

0

, CLK

Over the Operating Range (continued)

CO

1

)

, CLK

[5]

2

, or CLK

[5]

[5]

[5]

[5]

[5]

3

)

[5]

[5]

[5]

0

, CLK

[5]

Description

1

, CLK

[12]

2

, or CLK

CO

+ t

SCS

CO

IS

), 1/t

, 1/(t

3

Ultra37000 CPLD Family

+ t

) to Output Register Synchronous

S

ICS

S

) or 1/(t

+ t

, 1/(t

H

), or 1/t

WL

WL

+ t

+ t

CO

WH

WH

)

WL

[5]

), 1/(t

)

[5]

+ t

IS

WH

Page 18 of 64

+ t

),

IH

),

MHz

MHz

MHz

MHz

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns