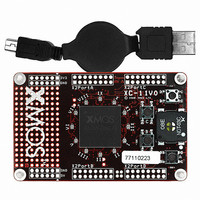

XCARD XC-1 XMOS, XCARD XC-1 Datasheet

XCARD XC-1

Specifications of XCARD XC-1

Related parts for XCARD XC-1

XCARD XC-1 Summary of contents

Page 1

... XS1-G4 144BGA Datasheet Publication Date: 2010/09/07 Copyright © 2010 XMOS Ltd. All Rights Reserved. Version 3.5 ...

Page 2

... A high performance switch supports low latency and deterministic communication between the threads in different XCores. The XMOS architecture is unique in its direct support for concurrent processing (multi-threading), event han- dling, communication and timed I/O operations. XS1-G4 Package Features Four XCores providing 1600MIPS and concurrent, deterministic real-time tasks 88 user I/O pins, dynamically confi ...

Page 3

... The following I/O type conventions are used in this document 1.1 XCore Signals XCore signals can be used for generic I/O ports or for XMOS Links. All the XCore signals are bidirectional and share the same electrical characteristics: Signal I/O X0D0 : X0D43 IO X2D0 : X2D43 IO 1.1.1 XCore signals as I/O ports The following table shows the I/O ports available on XCores 0 and 2 ...

Page 4

... The ports and links are multiplexed and follow a defined precedence if they overlap on the same core XMOS Link is enabled, the link has access to the pins; the pins of the underlying ports are disabled port is enabled, it overrules ports with higher widths that share the same pins ...

Page 5

... XnD36 A4 M9 XnD37 A5 M8 XnD38 A6 M7 XnD39 A7 M6 XnD40 A8 M5 XnD41 A9 M4 XnD42 A10 M3 XnD43 A11 M2 XMOS LINKS XCORE0, XCORE2 5bit 2bit 1b 4b P1A0 XLA4in P1B0 XLA3in P4A0 XLA2in P4A1 XLA1in XLA1in P4B0 XLA0in XLA0in P4B1 XLA0out XLA0out P4B2 XLA1out XLA1out ...

Page 6

... Core Power and Ground Pin Table Signal VDD VDD VDD VDD VDD VDD VDD VDD Ball ID Signal E4 SS_TDO E9 SS_TEST_ENA D4 SS_TMS D5 SS_TRST H9 SS_XC0_BS0 J8 Ball ID Signal C3 VSS C10 VSS D6 VSS F9 VSS G4 VSS J7 VSS K3 VSS K10 VSS VSS VSS VSS VSS VSS VSS VSS VSS www.xmos.com 6/22 Ball Ball ...

Page 7

... XS1-G4 144BGA Datasheet (3.5) 1.5 XCore I/O Power Table Signal IO VDD IO VDD IO VDD IO VDD IO VDD IO VDD IO VDD IO VDD 1.6 XMOS Link Pin Table See Section 1.2 Port Pin Table Ball ID Signal A1 IO VSS B6 IO VSS B11 IO VSS F2 IO VSS G11 IO VSS ...

Page 8

... AGND power supply for the PLL I, PD, ST Clock System clock I/O Function Description IO, PU Boot See Boot status pins below status XCore0 IO, PU, ST Debug Activates multicore debug I, PD, ST Reset Asynchronous system reset I, PD Reserved, tie to IO_VDD I, PD Reserved, tie pin to ground www.xmos.com 8/22 20 MHz are ...

Page 9

... SS_XC0_BS0 should be tied to IO_VDD. For further details on booting XCores see the XS1-G System Specification document (http://xmos.com/published/xsystem). SS_DEBUG This pin is used to synchronize the debugging of multiple G4 devices. This pin can operate in both output and input mode. In output mode and when configured to do so, SS_DEBUG is driven low by the device when one or more internal XCore processors hit a debug break point. Prior to this point the pin is tri-stated. In input mode and when confi ...

Page 10

... TRST Test reset (optional TDI Test data in OT, PU TDO Test data out Description See IEEE 1149.1 documentation Copies shared register contents, into data regis- ter (a=address register bits) Copies data register contents into shared regis- ter (a=address register bits) www.xmos.com 10/22 ...

Page 11

... XCore ID register RO XCore ID register RO XCore ID register RW Control internal switch permis- sions to debug register RW Trigger debug interrupts RO PLL clock divider register RO OTP security configuration reg- ister RO Internal link status RW Scratch register for debug soft- ware protocols RO Copy Copy of SR www.xmos.com 11/22 ...

Page 12

... Signal pin may be any pin except power supply pins MIN TYP 3.0 3.3 0.95 1.0 0.95 1.0 0.95 1.0 6.18 6.5 temperature 0 temperature -40 -65 MIN TYP 2.0 -0.3 2 www.xmos.com 12/22 MAX UNITS Notes 3 1. 1.05 V 1. Degrees C 85 Degrees C 125 ...

Page 13

... VDD supply. Specifically, the VDDIO and OTP_VDDIO supplies should rise to their nominal operating range with VDD held at 0V. The VDD supply should then rise to its nominal operating range with a rise time of less than 10ms. MIN TYP MAX 100 1 100 www.xmos.com 13/22 Notes UNITS Notes ...

Page 14

... XS1-G4 512BGA package or make provision for forced air and/or heatsinks in your PCB layout. MIN TYP 120 4 Commercial Qualification MIN TYP 1.6 Industrial Qualification MIN TYP 1.6 Note. For exceptional application loads www.xmos.com 14/22 MAX UNITS Notes mA mA MAX UNITS Notes Watts 1,2,3 MAX UNITS Notes ...

Page 15

... Internal one-time programmable memory Each XCore has 64K bits of one-time programmable memory that can be programmed using the JTAG interface. Note. MIN TYP MAX 12.5 20 100 1 2 MIN TYP MAX 400 www.xmos.com 15/22 UNITS Notes MHz 1 ns UNITS Notes MHz ...

Page 16

... Note that these parameters are specifi window rather than MIN TYP MAX 1 for more details. MIN TYP MAX www.xmos.com 16/22 UNITS Notes V/ s UNITS Notes ns ns MHz ...

Page 17

... XS1-G4 144BGA Datasheet (3.5) absolute numbers since the G4 provides functionality to delay the incoming clock with respect to the incoming data. For further details on these parameters and on interfacing to higher speed synchronous interfaces see the relevant application note. 3.9 XMOS Link Interface Performance Symbol Parameter B(2blink_5) ...

Page 18

... VSS SS_PLL VSS VSS VSS _AVDD SS_PLL SS_TMS SS_TDO VDD SS_TDI _LOCK X2D11 X2D10 X2D9 X2D8 X2D22 X2D21 IO VSS IO VDD X2D41 X2D40 X2D39 X2D38 www.xmos.com 18/ X0D40 X0D41 X0D42 X0D43 IO VSS X0D21 X0D22 X0D23 IO VDD X2D24 X0D10 X0D11 VDD X2D12 X2D25 SS_XC0 ...

Page 19

... XS1-G4 144BGA Datasheet (3.5) 4.2 Package Mechanical Details www.xmos.com 19/22 ...

Page 20

... JEDEC is an international organization that manages standards in the electronic and semiconductor industries. XMOS has a unique Manufacturers ID which is: 7F7F7F7F7F7F19H or: 01111111011111110111111101111111011111110111111100011000B 6.2 XMOS JTAG ID A modified version of the XMOS JEDEC Manufacturers ID is installed in the JTAG ID field. It appears in the JTAG ID as: Bit31 Unused Device Part No. 0 ...

Page 21

... XS1-G4 144BGA Datasheet (3.5) 7 Ordering information Part numbering and ordering information XMOS Ident & Architecture Family (G general purpose) XCore Tiles Variant (000 standard product) Revision Mask (A-Z) Package Type Pin Count Temp Grade (C commercial 0-70C) Speed Grade (4 normal speed) 7.1 Orderable part numbers ...

Page 22

... XMOS Ltd. is the owner or licensee of this design, code, or Information (collectively, the “Information”) and is providing it to you “AS IS” with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the Information, or any particular implementation thereof will be free from any claims of infringement and again, shall have no liability in relation to any such claims. Copyright © ...