LFE2M20E-5FN256I Lattice, LFE2M20E-5FN256I Datasheet - Page 86

LFE2M20E-5FN256I

Manufacturer Part Number

LFE2M20E-5FN256I

Description

IC FPGA 20KLUTS 140I/O 256-BGA

Manufacturer

Lattice

Datasheet

1.LFE2-12E-5FN256C.pdf

(385 pages)

Specifications of LFE2M20E-5FN256I

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFE2M20E-5FN256I

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

- Current page: 86 of 385

- Download datasheet (3Mb)

Lattice Semiconductor

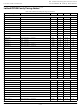

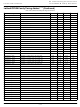

sysCLOCK GPLL Timing

f

f

f

f

f

AC Characteristics

t

t

t

t

t

t

t

t

t

t

t

t

1. Jitter sample is taken over 10,000 samples of the primary PLL output with clean reference clock and no additional I/O pins toggling.

2. Output clock is valid after t

3. Using LVDS output buffers.

4. Relative to CLKOP.

5. Value of external capacitor: 5.6 nF ±20%, NPO dielectric, ceramic chip capacitor, 1206 or smaller package, connected to PLLCAP pin.

6. f

Timing v.A 0.11

IN

OUT

OUT2

VCO

PFD

DT

PH

OPJIT

SK

W

LOCK

PA

IPJIT

FBKDLY

HI

LO

RST

Parameter

4

OUT

2

1

(max) = f

Input Clock Frequency (CLKI, CLKFB)

Output Clock Frequency (CLKOP,

CLKOS)

K-Divider Output Frequency (CLKOK)

PLL VCO Frequency

Phase Detector Input Frequency

Output Clock Duty Cycle

Output Phase Accuracy

Output Clock Period Jitter

Input Clock to Output Clock Skew

Output Clock Pulse Width

PLL Lock-in Time

Programmable Delay Unit

Input Clock Period Jitter

External Feedback Delay

Input Clock High Time

Input Clock Low Time

RST Pulse Width (RESETM/RESETK)

Reset Signal Pulse Width (CNTRST)

IN

* 10 for f

IN

LOCK

< 5MHz.

Description

for PLL reset and dynamic delay adjustment.

Over Recommended Operating Conditions

Without external capacitor

With external capacitor

Without external capacitor

With external capacitor

Without external capacitor

With external capacitor

Without external capacitor

With external capacitor

f

50 ≤ f

f

Without external capacitor

With external capacitor

Without external capacitor

With external capacitor

Default duty cycle selected

N/M = integer

At 90% or 10%

90% to 90%

10% to 10%

OUT

OUT

3-35

≥ 100 MHz

< 50 MHz

OUT

< 100 MHz

Conditions

DC and Switching Characteristics

LatticeECP2/M Family Data Sheet

5, 6

5

5

5, 6

5

5

3

0.156

0.039

Min.

640

500

0.5

0.5

20

20

20

45

85

15

20

—

—

—

—

—

—

—

—

—

2

5

2

1

Typ.

130

50

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

±0.05

0.025

Max.

1280

±125

±200

±250

0.04

420

420

420

210

420

150

500

360

50

25

50

55

10

—

—

—

—

—

—

Units

UIPP

UIPP

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

µs

µs

µs

ps

ps

ns

ps

ps

ns

ns

ns

ns

ns

%

UI

Related parts for LFE2M20E-5FN256I

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

FPGA - Field Programmable Gate Array 19K LUTs 304 I/O SERDES DSP -5

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 19K LUTs 140 I/O SERDES DSP -5

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 19K LUTs 304 I/O SERDES DSP -5

Manufacturer:

Lattice

Part Number:

Description:

FPGA - Field Programmable Gate Array 19K LUTs 304 I/O SERDES DSP -6

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 19K LUTs 140 I/O SERDES DSP -6

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

IC FPGA 20KLUTS 140I/O 256-BGA

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

IC FPGA 20KLUTS 140I/O 256-BGA

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

IC FPGA 20KLUTS 304I/O 484-BGA

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

IC FPGA 20KLUTS 140I/O 256-BGA

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

IC FPGA 20KLUTS 140I/O 256-BGA

Manufacturer:

Lattice

Datasheet:

Part Number:

Description:

IC FPGA 20KLUTS 304I/O 484-BGA

Manufacturer:

Lattice

Datasheet: