UPD70208HGF-10-3B9 NEC, UPD70208HGF-10-3B9 Datasheet

UPD70208HGF-10-3B9

Available stocks

Related parts for UPD70208HGF-10-3B9

UPD70208HGF-10-3B9 Summary of contents

Page 1

... MHz ( with 10/12.5/16/20 MHz supplied externally) The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information. Document No. U13225EJ4V0DS00 (4th edition) ...

Page 2

ORDERING INFORMATION (1) V40HL Part Number PD70208HGF-10-3B9 80-pin plastic QFP (14 (Resin thickness 2.7 mm) PD70208HGF-12-3B9 80-pin plastic QFP (14 (Resin thickness 2.7 mm) PD70208HGF-16-3B9 80-pin plastic QFP (14 (Resin thickness 2.7 mm) PD70208HGF-20-3B9 80-pin plastic QFP (14 (Resin thickness ...

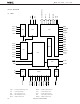

Page 3

PIN CONFIGURATION (Top View) (1) V40HL • 80-pin Plastic QFP (14 20 mm) PD70208HGF-10-3B9 PD70208HGF-12-3B9 PD70208HGF-16-3B9 PD70208HGF-20-3B9 A16/PS0 NC A15 A14 A13 A12 A11 A10 GND GND 13 AD7 14 AD6 15 AD5 16 ...

Page 4

Plastic TQFP (Fine pitch) (12 PD70208HGK-10-9EU PD70208HGK-12-9EU PD70208HGK-16-9EU PD70208HGK-20-9EU A15 A14 3 A13 4 A12 ...

Page 5

Plastic QFJ (950 950 mil) PD70208HLP-10 PD70208HLP-12 PD70208HLP-16 PD70208HLP- A15 10 A14 11 A13 12 A12 13 A11 14 A10 GND 18 AD7 19 AD6 20 AD5 21 ...

Page 6

V50HL • 80-pin Plastic QFP (14 20 mm) PD70216HGF-10-3B9 PD70216HGF-12-3B9 PD70216HGF-16-3B9 PD70216HGF-20-3B9 A16/PS0 NC AD15 AD14 AD13 AD12 AD11 AD10 AD9 AD8 GND NC GND AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NC NC END/ ...

Page 7

Plastic TQFP (Fine pitch) (12 PD70216HGK-10-9EU PD70216HGK-12-9EU PD70216HGK-16-9EU PD70216HGK-20-9EU AD15 AD14 3 AD13 4 AD12 ...

Page 8

Plastic QFJ (950 950 mil) PD70216HLP-10 PD70216HLP-12 PD70216HLP-16 PD70216HLP- AD15 10 AD14 11 AD13 12 AD12 13 AD11 14 AD10 15 AD9 16 AD8 17 GND 18 AD7 19 AD6 20 AD5 21 AD4 22 AD3 ...

Page 9

... Internally Connected INTAK/SRDY/TOUT1 : Interrupt Acknowledge/Serial Ready/Timer Output 1 INTP1-INTP7 : Interrupt Request from Peripherals IORD : I/O Read IOWR : I/O Write MRD : Memory Read MWR : Memory Write Connection NMI : Non-Maskable Interrupt Request POLL : Poll QS0, QS1 : Queue Status READY : Ready REFRQ : Refresh Request RESET : Reset RESOUT ...

Page 10

BLOCK DIAGRAM (1) V40HL TOUT2 TOUT1 TCU TCTL2 TCLK INTP7 INTP6 INTP5 ICU INTP4 INTP3 INTP2 INTP1 INTAK NMI CPU : Central Processing Unit CG : Clock Generator BIU : Bus Interface Unit BAU : Bus Arbitration ...

Page 11

V50HL TOUT2 TOUT1 TCU TCTL2 TCLK INTP7 INTP6 INTP5 ICU INTP4 INTP3 INTP2 INTP1 INTAK NMI SCU BIU WCU CPU BAU DMAU Data Sheet U13225EJ4V0DS00 PD70208H, 70216H POLL BUSLOCK BUFEN BUFR/W UBE ASTB IOWR IORD MWR ...

Page 12

DIFFERENCES FROM V40 AND V50 Item Operating supply voltage MAX. : 10, 12.5, 16, 20 MHz DD frequency MIN ...

Page 13

PIN FUNCTIONS ................................................................................................................................... 1.1 LIST OF PIN FUNCTIONS ........................................................................................................................... 1.2 PROCESSING OF UNUSED PINS .............................................................................................................. 2. MEMORY AND I/O CONFIGURATION ................................................................................................ 2.1 MEMORY SPACE ......................................................................................................................................... 2.2 I/O SPACE .................................................................................................................................................... 3. CPU ........................................................................................................................................................ 4. CG (CLOCK GENERATOR) ................................................................................................................. 5. BIU ...

Page 14

ELECTRICAL SPECIFICATIONS ......................................................................................................... 16 OPERATION .................................................................................................................................... 16 OPERATION .................................................................................................................................... 17. PACKAGE DRAWINGS ........................................................................................................................ 100 18. RECOMMENDED SOLDERING CONDITIONS ................................................................................... 103 14 Data Sheet U13225EJ4V0DS00 PD70208H, 70216H ...

Page 15

... These pins are provided with a latch. Therefore, when they go into a high-impedance state, they hold the status before the high-impedance state until driven by an external device not necessary to pull up or down the data bus. To invert the level of the pin that goes into a high-impedance state by an ...

Page 16

... DMA acknowledge 3/serial transmit data Input DMA request 3/serial receive data DMA acknowledge Input DMA request I/O DMA service forcible termination/DMA service completion — Positive power supply pin — Ground potential pin — Internal connection pin (External connection impossible) Data Sheet U13225EJ4V0DS00 PD70208H, 70216H Function ...

Page 17

... PROCESSING OF UNUSED PINS Table 1-1 shows the processing (recommended connection) of the unused pins. Use of a resistor with a resistance recommended to connect these pins to V Pin Name Input/Output Note 1 AD0 to AD15 3-state I/O Note 2 AD0 to AD7 3-state I/O Note A15 3-state output ...

Page 18

... Remark The circuit configuration of the latch is as illustrated below. To invert the level of the pin with a latch, a drive current higher than the latch invert current is necessary. (1) Output pin Output buffer Hi-Z control (2) I/O pin Output buffer Hi-Z control 18 Latch Latch Input buffer Data Sheet U13225EJ4V0DS00 ...

Page 19

MEMORY AND I/O CONFIGURATION 2.1 MEMORY SPACE The V40HL and V50HL can access a 1M-byte (512K-word) memory space. FFFFFH FFFFCH FFFFBH FFFF0H FFFEFH 00400H 003FFH 00000H Figure 2-2. Interface with Memory (1/2) A0-A19 D0-D7 Figure 2-1. Memory Map Reserved ...

Page 20

A1-A19 A0 UBE BSEL D0-D15 20 Figure 2-2. Interface with Memory (2/2) (b) V50HL Address Bus (19) 19 BSEL Memory Memory Upper Bank Lower Bank 512K Byte 512K Byte D8-D15 8 Data Bus (16) Data Sheet U13225EJ4V0DS00 PD70208H, 70216H 19 ...

Page 21

I/O SPACE In the V40HL and V50HL, I/ 64K bytes (32K words) can be accessed in an area independent of the memory. The various on-chip peripheral LSIs are set by accessing the system I/O area. Extended functions ...

Page 22

CPU The CPU has the same functions as the V20HL the use of the bus with on-chip peripherals, but in software terms the CPU is fully compatible. The internal block diagram of the CPU is shown in Figure 3-1. ...

Page 23

Figure 3-1. Internal Block Diagram of CPU (2/2) (b) V50HL Internal Address/Data Bus (20) ADM PS SS DS0 DS1 PFP DP TEMP ...

Page 24

... CG (CLOCK GENERATOR) The CG generates a clock at a frequency of 1/2, 1/4, 1/8 or 1/16 that of the crystal and oscillator connected to the X1 and X2 pins, supplies it as the CPU operating clock and outputs it externally as the CLKOUT pin output. The interrupt cycle time can be changed according to the oscillator scaling factor. The scaling factor can be set by a system I/O area register ...

Page 25

... A bus master such as the CPU, DMAU, REFU, etc., incorporated in the V40HL and V50HL normally release the bus at the end of the bus cycle currently being executed, as shown in Figure 6-1. However, in the case of a bus master connected to the HLDRQ pin, or cascaded external DMA controllers, for instance, the situation is as shown in Figure 6-2. The V40HL and V50HL request return of the bus by inactivating the acknowledge signal (HLDAK), and on receiving this request, the external bus master holding the bus should release the bus by dropping the bus hold request signal (HLDRQ) ...

Page 26

Bus Cycle Internal DMA Request Internal Refresh Request (Highest Priority) Bus Cycle HLDRQ Pin HLDAK Pin Internal Refresh Request (Highest Priority) Note The period in which the external bus master which has been given the bus after its release by ...

Page 27

WCU (WAIT CONTROL UNIT) The WCU has the function of automatically inserting a wait state (TW clock cycles in a CPU, DMAU or REFU bus cycle. 7.1 FEATURES • Automatic setting ...

Page 28

... RELATION BETWEEN WCU AND READY PIN When wait cycles exceeding 3 clock cycles are necessary, the WCU and the READY signal pin can be used in combination. The number of wait cycles specified by the WCU set value or the number of wait cycles under READY control, whichever is larger, is inserted. ...

Page 29

REFU (REFRESH CONTROL UNIT) The REFU generates refresh cycles required for refreshing of external DRAM. Refresh enabling/disabling and the refresh interval can be set programmably. 8.1 FEATURES • Lowest-priority refreshing/highest-priority refreshing • 7-refresh queue • 16-bit refresh address • ...

Page 30

TCU (TIMER/COUNTER UNIT) The TCU incorporates 3 counters, and can be used as a timer, event counter, rate generator, etc. Functionally subset of the PD71054. 9.1 FEATURES • 3 16-bit counters • Six programmable count modes ...

Page 31

SCU (SERIAL CONTROL UNIT) The SCU performs control of serial communication (asynchronous). Its functions are a subset of the PD71051 excluding synchronous communication. Also, what was the control word register in the PD71051 has been divided into two: a ...

Page 32

... V40HL and V50HL. 11.1 FEATURES • 8 interrupt inputs • PD71059 cascading possible • Edge- or level-triggered request input (input from internally connected TCU is edge-triggered only) • Interrupt requests individually maskable • Programmable interrupt request priority order • Polling operation capability 11.2 ICU INTERNAL BLOCK DIAGRAM ...

Page 33

DMAU (DMA CONTROL UNIT) The DMAU has 4 DMA channels, and provides the functions (subset) of two LSIs, the PD71071 and PD71037. 12.1 FEATURES • Two operating modes ( PD71071 mode, PD71037 mode) • 20-bit address register • 16-bit ...

Page 34

... STOP mode When the HALT instruction is executed, all clocks to the CPU and internal I/Os are stopped. STOP mode should be used when a resonator is connected to the X1 and X2 pins. Remark Switching between HALT mode and STOP mode is performed by setting a system I/O area register. 14. RESET OPERATION When the RESET pin is driven low and this level is held for 4 clock cycles or more from the fall of the signal, the CPU and on-chip peripheral LSIs are reset ...

Page 35

INSTRUCTION SET Identifier reg 8/16-bit general register (destination register in an instruction using two 8/16-bit general registers) reg’ Source register in an instruction using two 8/16-bit general registers reg8 8-bit general register (destination register in an instruction using two ...

Page 36

Identifier W Byte/word specification bit (0: byte, 1: word). However, when s =1, byte data of sign extension is 16-bit operand reg Register field (000 to 111) reg’ Register field (000 to 111) (source register in ...

Page 37

Table 15-3. Operand Description Legend Identifier AW Accumulator (16-bit) AH Accumulator (high-order byte) AL Accumulator (low-order byte) BW Register BW (16-bit) CW Register CW (16-bit) CL Register CL (low-order byte) DW Register DW (16-bit) BP Base pointer (16-bit) SP Stack ...

Page 38

Identifier (Blank mod 00 mem 000 001 010 011 100 IX 101 IY 110 DIRECT ADDRESS 111 BW Table 15-6. 8/16-Bit General Register Selection ...

Page 39

The instruction set is shown in tabular form on the following pages. Clock cycle shown in table is the time required for execution of instruction by the execution unit and is based on the following conditions. • Prefetch time and ...

Page 40

V50HL On the left of "/" : The value corresponding to byte processing ( word processing ( even address On the right of "/" : The value corresponding to word processing (W =1) of ...

Page 41

Instruc- Operation Code tion Mnemonic Operand(s) Group MOV reg, reg’ mem, reg 1 0 ...

Page 42

Instruc- Operation Code tion Mnemonic Operand(s) Group REPC REPNC ...

Page 43

Instruc- Operation Code tion Mnemonic Operand(s) Group INS reg8, reg8’ ...

Page 44

Instruc- Operation Code tion Mnemonic Operand(s) Group ADD reg, reg’ reg reg’ mem, reg ...

Page 45

Instruc- Operation Code tion Mnemonic Operand(s) Group ADD4S ...

Page 46

Instruc- Operation Code tion Mnemonic Operand(s) Group MULU reg8 reg mem8 ...

Page 47

Instruc- Operation Code tion Mnemonic Operand(s) Group DIVU reg8 reg mem8 ...

Page 48

Instruc- Operation Code tion Mnemonic Operand(s) Group reg8 reg DIV mem8 ...

Page 49

Instruc- Operation Code tion Mnemonic Operand(s) Group ADJBA ADJ4A ...

Page 50

Instruc- Operation Code tion Mnemonic Operand(s) Group TEST reg, reg’ mem, reg 1 0 ...

Page 51

Instruc- Operation Code tion Mnemonic Operand(s) Group TEST1 reg8 reg ...

Page 52

Instruc- Operation Code tion Mnemonic Operand(s) Group CLR1 reg8 reg ...

Page 53

Instruc- Operation Code Mnemonic Operand(s) tion Group SHL reg reg ...

Page 54

Instruc- Operation Code Mnemonic Operand(s) tion Group SHR reg reg ...

Page 55

Instruc- Operation Code Mnemonic tion Operand(s) Group SHRA reg reg ...

Page 56

Instruc- Operation Code tion Mnemonic Operand(s) Group ROL reg reg ...

Page 57

Instruc- Operation Code tion Mnemonic Operand(s) Group ROR reg reg ...

Page 58

Instruc- Operation Code tion Mnemonic Operand(s) Group ROLC reg reg ...

Page 59

Instruc- Operation Code tion Mnemonic Operand(s) Group RORC reg reg ...

Page 60

Instruc- Operation Code Mnemonic Operand(s) tion Group CALL near-proc regptr16 ...

Page 61

Instruc- Operation Code tion Mnemonic Operand(s) Group PUSH mem16 mod mem reg16 0 ...

Page 62

Instruc- Operation Code tion Mnemonic Operand(s) Group near-label short-label ...

Page 63

Instruc- Operation Code tion Mnemonic Operand(s) Group short-label BNV short-label ...

Page 64

Instruc- Operation Code Mnemonic Operand(s) tion Group BRK imm8 ...

Page 65

Instruc- Operation Code tion Mnemonic Operand(s) Group HALT POLL ...

Page 66

... Output voltage Operating ambient temperature Storage temperature Cautions 1. Do not directly connect the output pins of two or more IC products and do not directly connect the output pins to V connected directly. Moreover, an external circuit whose timing is designed to avoid output collision can be connected to pins that go into a high-impedance state. ...

Page 67

DC CHARACTERISTICS (T = – 10% ( PD70208H, 70216H-10/12/16 Parameter Symbol Input voltage high V Input voltage low V Clock input voltage high V Clock input voltage low V Output ...

Page 68

AC CHARACTERISTICS (1) PD70208H, 70216H-10/12/ Parameter External clock input cycle External clock input high-level width (V =3 External clock input low-level width (V =1 External clock input rise time (1.5 3.0 V) External clock ...

Page 69

... SEDK <65> EDEDL <66> SDQK <67> IPIPL <68> t 500 SRX pull-up resistor is connected.) pull-up resistor is connected.) Data Sheet U13225EJ4V0DS00 PD70208H, 70216H Output Pin Load Capacitance 100 pF L PD70208H-12 PD70208H-16 PD70216H-12 PD70216H-16 Unit MIN. MAX. MIN. MAX –10 t –10 ...

Page 70

... Specification to guarantee that REFRQ is always later than MRD . Only guaranteed when the EREF bit of the SCTL register When using internal clock generator by connecting a resonator to the X1 and X2 pins, the oscillation stabilization time must be added at power-ON. Because the oscillation stabilization time varies depending on the characteristics of the resonator and oscillator used, evaluate the oscillation stabilization time with the resonator and oscillator actually used ...

Page 71

PD70208H, 70216H- – Parameter External clock input cycle External clock input high-level width (V =3 External clock input low-level width (V =1 External clock input rise time (1.5 ...

Page 72

... DMA extended write <56> DMA normal write <57> <58> <59> <60> <61> <62> <63> <64> <65> <66> <67> <68> <69> <70> pull-up resistor is connected) Data Sheet U13225EJ4V0DS00 PD70208H, 70216H = 100 pF L PD70208H-20 Symbol PD70216H-20 Unit MIN. MAX –10 ns HSTA KKH DKCT1 DKCT2 ...

Page 73

... This rating is to guarantee that REFRQ bit of the STCL register When using internal clock generator by connecting a resonator to the X1 and X2 pins, the oscillation stabilization time must be added at power-ON. Because the oscillation stabilization time varies depending on the characteristics of the resonator and oscillator used, evaluate the oscillation stabilization time with the resonator and oscillator actually used ...

Page 74

... RECOMMENDED OSCILLATOR The clock input circuits (1) and (2) shown below are recommended. (1) Ceramic resonator connection (T ( PD70208H, 70216H-20)) Cautions 1. The oscillator should be as close as possible to the X1 and X2 pins other signal lines should pass through the area enclosed in dashed line. 3. For matching between V40HL, V50HL and resonator, the efficient evaluation should be carried out ...

Page 75

... Clock input voltage Output voltage Operating ambient temperature Storage temperature Cautions 1. Do not directly connect the output pins of two or more IC products and do not directly connect the output pins connected directly. Moreover, an external circuit whose timing is designed to avoid output collision can be connected to pins that go into a high-impedance state. ...

Page 76

DC CHARACTERISTICS (T = – Parameter Symbol Input voltage high V Input voltage low V Clock input voltage high V Clock input voltage low V Output voltage high V Output voltage low V Input leak ...

Page 77

AC CHARACTERISTICS (1) PD70208H, 70216H-10/12/ Parameter External clock input cycle External clock input high-level width (V =0 External clock input low-level width (V =0 External clock input rise time (0 ...

Page 78

... SDQK <67> t 100 IPIPL <68> t 1000 SRX <69> t 1000 HRX <70> t 150 DKSR pull-up resistor is connected) pull-up resistor is connected) Data Sheet U13225EJ4V0DS00 PD70208H, 70216H Output Pin Load Capacitance 100 pF L PD70208H-12 PD70208H-16 PD70216H-12 PD70216H-16 Unit MIN. MAX. MIN. MAX. t –30 t –20 ns KKH KKH ...

Page 79

... Specification to guarantee that REFRQ is always later than MRD . Only guaranteed when the EREF bit of the SCTL register When using internal clock generator by connecting a resonator to the X1 and X2 pins, the oscillation stabilization time must be added at power-ON. Because the oscillation stabilization time varies depending on the characteristics of the resonator and oscillator used, evaluate the oscillation stabilization time with the resonator and oscillator actually used ...

Page 80

PD70208H, 70216H- – Parameter External clock input cycle External clock input high-level width (V =0 External clock input low-level width (V =0 External clock input rise time (0.2 ...

Page 81

... DMA extended write <55> DMA normal write <56> <57> <58> <59> <60> <61> <62> <63> <64> <65> <66> <67> <68> <69> <70> pull-up resistor is connected) Data Sheet U13225EJ4V0DS00 PD70208H, 70216H = 100 pF L PD70208H-20 Symbol PD70216H-20 Unit MIN. MAX –20 ns HSTA KKH DKCT1 DKCT2 ...

Page 82

... This rating is to guarantee that REFRQ bit of the STCL register When using internal clock generator by connecting a resonator to the X1 and X2 pins, the oscillation stabilization time must be added at power-ON. Because the oscillation stabilization time varies depending on the characteristics of the resonator and oscillator used, evaluate the oscillation stabilization time with the resonator and oscillator actually used ...

Page 83

... RECOMMENDED OSCILLATOR The clock input circuits (1) and (2) shown below are recommended. (1) Ceramic resonator connection (T Cautions 1. The oscillator should be as close as possible to the X1 and X2 pins other signal lines should pass through the area enclosed in dashed line. 3. V40HL, V50HL and resonator matching requires careful evaluation. ...

Page 84

AC Test Input Waveform (Except X1 and X2) ( operation) 2 Test Output Test Points ( operation) AC Test Input Waveform (Except X1 and X2) ( operation) 0 ...

Page 85

Clock Timing External Clock (Input) (X1) <11> CLKOUT (Output) Reset Timing CLKOUT (Output) <16> RESET (Input) RESOUT (Output) Ready Timing (1) T1 CLKOUT (Output) READY (Input) Variation Range Ready Timing (2) T1 CLKOUT (Output) <19> READY (Input) Variation Range Note ...

Page 86

Read Timing T4 CLKOUT (Output) 27 A16/PS0- A19/PS3 (Output) 27 A8-A15 (Output): V40HL UBE (Output): V50HL 27 AD0-AD7 (I/O): V40HL AD0-AD15 (I/O): V50HL 33 ASTB (Output) BUFEN (Output) 38 BUFR/W (Output) MRD (Output) IORD (Output) BS0-BS2 (Output) 49 Note High-level ...

Page 87

Write Timing T4 CLKOUT (Output) 27> A16/PS0- A19/PS3 (Output) 27 A8-A15 (Output): V40HL UBE (Output): V50HL 27 AD0-AD7 (I/O): V40HL AD0-AD15 (I/O): V50HL ASTB (Output) 33 BUFEN (Output) 38 BUFR/W (Output) MWR (Output) IOWR (Output) BS0-BS2 (Output) 49 Note High-level ...

Page 88

Status Timing T4 CLKOUT (Output) 27 A16/PS0- A19/PS3 (Output) 27 A8-A15 (Output): V40HL UBE (Output): V50HL 27 AD0-AD7 (I/O): V40HL AD0-AD15 (I/O): V50HL 33 ASTB (Output) BS0-BS2 (Output) 49 Note 1 27 QS0, QS1 (Output) Notes 1. MRD, IORD, MWR, ...

Page 89

Interrupt Acknowledge Timing (V40HL) T1 CLKOUT (Output) A8-A15 (Output) <32> AD0-AD7 (I/O) ASTB (Output) <38> INTAK (Output) BUFEN (Output) BUFR/W (Output) BUSLOCK (Output) Notes 1. Slave address in case of interrupt from external PD71059. Invalid data in case of interrupt ...

Page 90

Interrupt Acknowledge Timing (V50HL) T1 CLKOUT (Output) <32> AD0-AD15 (I/O) ASTB (Output) <38> INTAK (Output) <38> BUFEN (Output) BUFR/W (Output) BUSLOCK (Output) Notes 1. Slave address in case of interrupt from external PD71059. Invalid data in case of interrupt from ...

Page 91

HLDRQ/HLDAK Timing (1) CLKOUT (Output) <51> HLDRQ (Input) HLDAK (Output) Note BS0-BS2 (Output) Note A16/PS0 to A19/PS3, UBE, BUFEN, BUFR/W, MRD, IORD, MWR, IOWR (all output): V40HL, V50HL A8-A15 (output): V40HL AD0-AD7 (input/output): V40HL AD0-AD15 (input/output) V50HL Remark A dashed ...

Page 92

POLL, NMI Input Timing CLKOUT (Output) POLL (Input) NMI (Input) BUSLOCK Output Timing CLKOUT (Output) <27> BUSLOCK (Output) Access Interval MRD (Output) IORD (Output) MWR (Output) IOWR (Output <24> <23> <86> <86> <86> <86> Data Sheet U13225EJ4V0DS00 PD70208H, ...

Page 93

Refresh Timing (V40HL) T4 CLKOUT (Output) 27 A16/PS0- A19/PS3 (Output) 27 A8-A15 (Output) 27 AD0-AD7 (I/O) 33 ASTB (Output) BUFEN (Output) MRD (Output) REFRQ (Output) 49 BS0-BS2 (Output) Remark A dashed line indicates high impedance ...

Page 94

Refresh Timing (V50HL) T4 CLKOUT (Output) 27 A16/PS0- A19/PS3 (Output) 27 UBE (Output) 27 AD0-AD15 (I/O) 33 ASTB (Output) BUFEN (Output) MRD (Output) REFRQ (Output) 49 BS0-BS2 (Output) Remark A dashed line indicates high impedance ...

Page 95

TCU Timing (1) CLKOUT (Output) <72> TCTL2 (Input) TOUTn (Output) (n=1, 2) Note Applies to TOUT2 output. TCU Timing (2) <82> <81> TCLK (Input) TCTL2 (Input) TOUTn (Output) (n=1, 2) Note Applies to TOUT2 output. <74> <77> <76> Note <80> ...

Page 96

SCU Timing RxD (Input) TOUT1 (Output) TxD (Output) CLKOUT (Output) SRDY (Output) 96 <68> <69> 16 Cycles or 64 Cycles 16 Cycles or 64 Cycles <71> <70> Data Sheet U13225EJ4V0DS00 PD70208H, 70216H ...

Page 97

DMAU Timing (1) T4 CLKOUT (Output) 49 BS0-BS2 (Output) 33 ASTB (Output) 27 A16/PS0- A19/PS3 (Output) 27 A8-A15 (Output): V40HL UBE (Output): V50HL 27 AD0-AD7 (I/O): V40HL AD0-AD15 (I/O): V50HL DMAAK (Output) MRD (Output) IORD (Output) MWR (Output) IOWR (Output) ...

Page 98

DMAU Timing (2) T1 CLKOUT (Output) TC (Input/Output) END (Input/Output) CLKOUT (Output) DMARQn (Input) (n=0- <60> <64> <62> <65> <66> Data Sheet U13225EJ4V0DS00 PD70208H, 70216H T4 <61> <63> ...

Page 99

DMAU Timing (3) (Cascade Mode) In Normal Operation: CLKOUT (Output) DMARQ (Input) DMAAK (Output) When Refresh Cycle is Inserted: CLKOUT (Output) DMARQ (Input) DMAAK (Output) ICU Timing INTPn (Input) (n=1-7) T1 <66> <66> <54> <54> <67> Data Sheet U13225EJ4V0DS00 PD70208H, ...

Page 100

PACKAGE DRAWINGS 80 PIN PLASTIC QFP (14x20 NOTE 1. Controlling dimension millimeter. 2. Each lead centerline is located within 0.15 mm (0.006 inch) of its true position (T.P.) at maximum material condition. ...

Page 101

PIN PLASTIC TQFP (FINE PITCH NOTE Each lead centerline is located within 0.10 mm (0.004 inch) of its true position (T.P.) at maximum material condition ...

Page 102

PIN PLASTIC QFJ (950 x 950 mil NOTES 1. Controlling dimension 2. Each lead centerline is located within 0. its true position (T.P.) at maximum material condition. 102 ...

Page 103

... Solder bath temperature: 260 C max. Time: 10 sec. max., Number of times: 1, Preheating temperature: 120 C max. (Package surface temperature), Number of Note days : 7 days (after this, prebaking is necessary at 125 C for 10 hours). Partial pin heating Pin temperature: 300 C max., Time: 3 sec. max. (per device side) ( masks ...

Page 104

L, F masks Soldering Method Infrared reflow Package peak temperature: 235 C, Time: 30 sec. max. (210 ˚C min.), Number of times: 3 max. VPS Package peak temperature: 215 C, Time: 40 sec. (200 C min.) Number of times: ...

Page 105

... Soldering Conditions Note : 1 day (after this, prebaking is necessary Note : 1 day (after this, prebaking is necessary Soldering Conditions Note : 7 days (after this, prebaking is Note : 7 days (after this prebaking is necessary at 125 C Data Sheet U13225EJ4V0DS00 PD70208H, 70216H Recommended Conditions Symbol IR30-101-1 VP15-101-1 — Recommended Conditions Symbol ...

Page 106

... Soldering Conditions Note : 7 days (after this, prebaking is necessary Note : 7 days (after this, prebaking is necessary Soldering Conditions Note : 7 days (after this, prebaking is Note : 7 days (after this prebaking is Data Sheet U13225EJ4V0DS00 PD70208H, 70216H ...

Page 107

Data Sheet U13225EJ4V0DS00 PD70208H, 70216H 107 ...

Page 108

... HANDLING OF UNUSED INPUT PINS FOR CMOS Note: No connection for CMOS device inputs can be cause of malfunction connection is provided to the input pins possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry ...

Page 109

... Regional Information Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify: • Device availability • Ordering information • ...

Page 110

... Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc. The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance ...