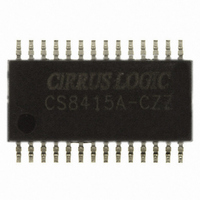

CS8415A-CZZ Cirrus Logic Inc, CS8415A-CZZ Datasheet

CS8415A-CZZ

Specifications of CS8415A-CZZ

Available stocks

Related parts for CS8415A-CZZ

CS8415A-CZZ Summary of contents

Page 1

... Stand-alone operation allows systems with no micro- controller to operate the CS8415A with dedicated output pins for channel status data. The CS8415A is available in a 28-pin TSSOP and SOIC package in both Commerical (-10 to +70°C) and Indus- trial grades (-40 to +85° C). The CDB8415A Customer Demonstration board is also available for device evalu- ation and implementation suggestions ...

Page 2

... Grade Range Commercial -10 to +70°C 28- Industrial -40 to +85° CS8415A Pb-Free Container Order Number Rail CS8415A-CZZ YES Tape and Reel CS8415A-CZZR Rail CS8415A-CZ NO Tape and Reel CS8415A-CZR Rail CS8415A-IZZ YES Tape and Reel CS8415A-IZZR Rail CS8415A-CSZ YES Tape and Reel CS8415A-CSZR Rail ...

Page 3

... Q-Channel Subcode Bytes (14h - 1Dh) (Read Only) ........................................................ 28 8.17 OMCK/RMCK Ratio (1Eh) (Read Only) ...................................................................................... 28 8.18 C-bit or U-bit Data Buffer (20h - 37h) .......................................................................................... 28 8.19 CS8415A I.D. and Version Register (7Fh) (Read Only) ............................................................. 28 9. PIN DESCRIPTION - SOFTWARE MODE .......................................................................................... 29 10. HARDWARE MODE .......................................................................................................................... 31 10.1 Serial Audio Port Formats .......................................................................................................... 31 11 ...

Page 4

... APPENDIX C: PLL FILTER ............................................................................................................... 40 15.1 General ....................................................................................................................................... 40 15.2 External Filter Components ........................................................................................................ 41 15.2.1 General .......................................................................................................................... 41 15.2.2 Capacitor Selection ........................................................................................................ 41 15.2.3 Circuit Board Layout ...................................................................................................... 41 15.3 Component Value Selection ....................................................................................................... 42 15.3.1 Identifying the Part Revision .......................................................................................... 42 15.3.2 External Components .................................................................................................... 42 15.3.3 Jitter Tolerance .............................................................................................................. 43 15.3.4 Jitter Attenuation ............................................................................................................ 44 16. REVISION HISTORY ........................................................................................................................ 45 4 CS8415A DS470F4 ...

Page 5

... Figure 22. Revision A1............................................................................................................................... 44 Figure 23. Revision A2 using A1 Values.................................................................................................... 44 Figure 24. Revision A2 using A2* Values .................................................................................................. 44 LIST OF TABLES Table 1. Control Register Map Summary................................................................................................... 20 Table 2. Equivalent Software Mode Bit Definitions .................................................................................... 31 Table 3. Hardware Mode Start-Up Options................................................................................................ 31 Table 4. Second Line Part Marking............................................................................................................ 42 Table kHz ........................................................................................................................... 42 Table kHz ......................................................................................................................... 42 Table 7. Revision History ........................................................................................................................... 45 DS470F4 CS8415A 5 ...

Page 6

... T -10 Commercial Grade A Industrial Grade -40 Symbol VL+,VA+ (Note stg Symbol VA+ VL+ = 3.3 V VL+ = 5.0 V VA+ VL+ = 3.3 V VL+ = 5.0 V VA+ VL+ = 3.3 V VL+ = 5.0 V CS8415A Typ Max Units 5.0 5.5 V 3.3 or 5.0 5 +70 °C - +85 Min Max Units - 6 ±10 mA -0.3 (VL+) + 0.3 V -55 125 ° ...

Page 7

... PLL Clock Recovery Sample Rate Range RMCK output jitter RMCK output duty cycle 6. Cycle-to-cycle using kHz external PLL filter components. DS470F4 Symbol Symbol (Note =0.4 V (Max pF. L Symbol (Note 6) CS8415A Min Typ Max Units µA - ±1 ±10 - 200 - mV Min Max Units (VL 0.4 V 2.0 (VL+) + 0.3 V -0.3 ...

Page 8

... L Symbol (Note 7) t dpd (Note 7) t smd (Note 8) t lmd (Note 9) t sckw t sckl t sckh (Note , , ) t lrckd t lrcks Notes OLRCK (input) t lrckd OSCLK t (input SDOUT Figure 2. Audio Port Slave Mode and Data Input Timing CS8415A Min Typ Max Units - - lrcks ...

Page 9

... Data must be held for sufficient time to bridge the transition time of CCLK. 14. For f <1 MHz. sck CS CCLK CDIN CDOUT DS470F4 = 20 pF. L Symbol (Note 12) f sck t csh t css t scl t sch t dsu (Note 13 (Note 14 (Note 14 scl t sch t css dsu Figure 3. SPI Mode Timing CS8415A Min Typ Max Units 0 - 6.0 MHz µs 1 100 ns ...

Page 10

... SCL t low pF. L Symbol fscl t buf t hdst t low t high t sust (Note 16) t hdd t sud susp Repeated Start t high t t sud t sust hdd Figure 4. I²C Mode Timing CS8415A Min Typ Max Units - - 100 kHz µs 4 µs 4 µs 4 µs 4 µs 4 µ 250 - - ns ...

Page 11

... F VA+ VL+ CS8415A RXP6 RXP5 OLRCK RXP4 OSCLK RXP3 SDOUT RXP2 RXP1 RXP0 RXN0 SDA/CDOUT AD0/CS RMCK SCL/CCLK AD1/CDIN INT U EMPH / DGND2 RERR H/S RST AGND FILT DGND RFILT CFILT CRIP CS8415A +3 +5.0 V Digital Supply 3-wire Serial Audio Input Device Microcontroller 11 ...

Page 12

... GENERAL DESCRIPTION The CS8415A is a monolithic CMOS device which receives and decodes audio data according to the AES3, IEC60958, S/PDIF, and EIAJ CP1201 interface standards. Input data is either differential or single-ended. A low-jitter clock is recovered from the incoming data using a PLL. The decoded audio data is output through a configurable, 3-wire output port. The channel status and user data are assembled in block-sized buffers and may be accessed through an SPI or I² ...

Page 13

... By appropri- ate phasing of the left/right clock and control of the serial clocks, multiple CS8415As can share one serial port. The left/right clock should be continuous, but the duty cycle can be less than the specified typical value of 50% if enough serial clocks are present in each phase to clock all the data bits ...

Page 14

... The CS8415A allows immediate mute of the serial audio output port audio data by the MUTESAO bit of Control Register 1. OLRCK Left Justified OSCLK (Out) SDOUT MSB OLRCK I²S OSCLK (Out) SDOUT MSB OLRCK Right Justified OSCLK (Out) SDOUT ...

Page 15

... RXN0, a PLL-based clock recovery circuit, and a decoder which separates the audio data from the channel status and user data. External components are used to terminate and isolate the incoming data cables from the CS8415A. These com- ponents are detailed in Appendix A. 5.1 ...

Page 16

... MPEG encoders, may not adhere to this convention, and the bit may not be properly set. The CS8415A AES3 receiver can detect such non-audio data. This is accomplished by looking for a 96-bit sync code, consisting of 0x0000, 0x0000, 0x0000, 0x0000, 0xF872, and 0x4E1F. When the sync code is detect- ed, an internal AUTODETECT signal will be asserted ...

Page 17

... SDOUT. Similarly, sub-frame B data will be routed to both the left and right data fields of the next word clock cycle of SDOUT. Using mono mode is only necessary if the serial audio output port must run at 96 kHz. If the CS8415A is kept in normal stereo mode, and receives AES3 data arranged in mono mode, then the serial audio output port will run at 48 kHz, with left and right data fields representing consecutive audio samples ...

Page 18

... The control port has 2 modes: SPI and I²C, with the CS8415A acting as a slave device. SPI mode is selected if there is a high-to-low transition on the AD0/CS pin, after the RST pin has been brought high. I²C mode is selected by connecting the AD0/CS pin to VL+ or DGND, thereby permanently selecting the desired AD0 bit address state ...

Page 19

... VL+ or DGND as desired. The EMPH pin is used to set the AD2 bit by connecting a resistor from the EMPH pin to VL DGND. The state of the pin is sensed while the CS8415A is being reset. The upper 4 bits of the 7-bit address field are fixed at 0010b. To communicate with a CS8415A, the chip address field, which is the first byte sent to the CS8415A, should match 0010b followed by the settings of the EMPH, AD1, and AD0 ...

Page 20

... INCR - Auto Increment Address Control Bit Default = ‘0’ Disabled 1 - Enabled MAP6:MAP0 - Register address Note: Reserved registers must not be written to during normal operation. Some reserved registers are used for test modes, which can completely alter the normal operation of the CS8415A SWCLK ...

Page 21

... Default = ‘0’ Normal stereo operation and B subframes treated as consecutive samples of one channel of data. Data is duplicated to both left and right parallel outputs of the AES receiver block. The sample rate (Fs) is doubled compared to MMR=0 DS470F4 RMCKF MMR CS8415A INT1 INT0 MUX2 MUX1 MUX0 21 ...

Page 22

... Reading and writing the U and C data buffers is not possible. Pow- er consumption is low Normal part operation. This bit must be written to the 1 state to allow the CS8415A to begin operation. All input clocks should be stable in frequency and phase when RUN is set to 1. ...

Page 23

... Indicates the completion C-buffer transfer. See “Channel Status and User Data Buffer Manage- ment” on page 38 for more information. RERR - A receiver error has occurred. The Receiver Error register may be read to determine the nature of the error which caused the interrupt. DS470F4 CS8415A DETC 0 RERR 23 ...

Page 24

... INT pin or the status register. The bit positions align with the corresponding bits in Interrupt 2 register. This register defaults to 00h DETU DETUM CS8415A QCH DETCM 0 RERRM DETC1 0 RERR1 DETC0 0 RERR0 QCHM 0 DS470F4 ...

Page 25

... COPY - SCMS copyright indicator 0 - Copyright asserted 1 - Copyright not asserted If the category code is set to General in the incoming AES3 stream, copyright will always be indicated by COPY, even when the stream indicates no copyright. DS470F4 DETU1 0 0 DETU0 AUX0 PRO CS8415A QCH1 0 0 QCH0 AUDIO COPY ORIG 25 ...

Page 26

... Confidence error. This is the logical OR of BIP and UNLOCK. BIP - Bi-phase error bit. Updated on sub-frame boundaries error 1 - Bi-phase error. This indicates an error in the received bi-phase coding. PAR - Parity bit. Updated on sub-frame boundaries error 1 - Parity error UNLOCK V CS8415A CONF BIP PAR DS470F4 ...

Page 27

... A information is output during control port reads when CAM is set to 0 (One Byte Mode Channel B information is displayed at the EMPH pin and in the receiver channel status register. Channel B information is output during control port reads when CAM is set to 0 (One Byte Mode) DS470F4 UNLOCKM CBMR DETCI CS8415A CONFM BIPM PARM CAM CHS 27 ...

Page 28

... CONTROL ADDRESS TRACK TRACK INDEX INDEX MINUTE MINUTE SECOND SECOND FRAME FRAME ZERO ZERO ABS FRAME ABS FRAME ORR4 ORR3 CS8415A DETUI ADDRESS ADDRESS ADDRESS TRACK TRACK TRACK INDEX INDEX INDEX MINUTE MINUTE MINUTE SECOND SECOND SECOND FRAME FRAME FRAME ZERO ...

Page 29

... CS8415A I.D. and Version Register (7Fh) (Read Only ID3 ID2 ID3 code for the CS8415A. Permanently set to 0100 VER3:0 - CS8415A revision level. Revision A is coded as 0001 DS470F4 ID1 ID0 VER3 CS8415A VER2 VER1 VER0 29 ...

Page 30

... CS8415A Address Bit 0 (I²C) / Control Port Chip Select (SPI) (Input falling edge on this pin puts the CS8415A into SPI control port mode. With no falling edge, the CS8415A defaults to I²C mode. In I²C 2 AD0/CS mode, AD0 is a chip address pin ...

Page 31

... VL+ Positive Digital Power (Input) - Positive supply for the digital section. Typically +3 +5.0 V. Hardware/Software Mode Control (Input) - Determines the method of controlling the operation of the CS8415A, and the method of accessing CS and U data. In software mode, device control and CS and U 24 H/S data access is primarily through the control port, using a microcontroller. Hardware mode provides an alternate mode of operation and access to the CS and U data through dedicated pins ...

Page 32

... MODE The CS8415A has a hardware mode which allows using the device without a microcontroller. Hardware mode is selected by connecting the H/S pin to VL+. Various pins change function in hardware mode, described in the hard- ware mode pin definition section. Hardware mode data flow is shown in serial audio output port ...

Page 33

... FILT dix C: PLL Filter” on page 41 Reset (Input) - When RST is low, the CS8415A enters a low power mode and all internal states are reset. On initial power up, RST must be held low until the power supply is stable, and all input clocks are stable in 9 RST frequency and phase ...

Page 34

... DGND 22 Hardware/Software Mode Control (Input) - Determines the method of controlling the operation of the CS8415A, and the method of accessing CS and U data. In software mode, device control and CS and U 24 H/S data access is primarily through the control port, using a microcontroller. Hardware mode provides an alter- nate mode of operation and access to the CS and U data through dedicated pins ...

Page 35

... The pins are then switched to be outputs. This mechanism allows output pins to be used to set alternative modes in the CS8415A by connecting a 47 kΩ resistor to between the pin and either VL+ (HI) or DGND (LO). For each mode, every start-up option select pin MUST have an external pull-up or pull-down resistor. In software mode, the only start-up option pin is EMPH, which is used to set a chip ad- dress bit for the control port in I² ...

Page 36

... AES3 Receiver External Components The CS8415A AES3 receiver is designed to accept both the professional and consumer interfaces. The dig- ital audio specifications for professional use call for a balanced receiver, using XLR connectors, with 110 Ω ±20% impedance. The XLR connector on the receiver should have female pins with a male shell. Since the receiver has a very high input impedance, a 110 Ω ...

Page 37

... Figure 15. TTL/CMOS Input Circuit CS8415A CS8415A µ 0. See Text RXP0 110 Ω µ 0.01 F RXN0 1 .01µF 75 Ω 75 Ω Coax .01µF 75 Ω 75 Ω Coax .01µF 75 Ω 75 Ω Coax .01µF Figure 14. S/PDIF MUX Input Circuit CS8415A RXP0 RXN0 RXP6 RXP5 . . . RXP0 RXN0 37 ...

Page 38

... AES3 Channel Status (C) Bit Management The CS8415A contains sufficient RAM to store a full block of C data for both A and B channels (192 384 bits), and also 384 bits of U information. The user may read from these buffer RAMs through the control port. ...

Page 39

... Return 14.2.1 Reserving the First 5 Bytes in the E Buffer D-to-E buffer transfers periodically overwrite the data stored in the E buffer. The CS8415A has the capa- bility of reserving the first 5 bytes of the E buffer for user writes only. When this capability is in use, internal D-to-E buffer transfers will NOT affect the first 5 bytes of the E buffer. Therefore, the user can set values in these first 5 E bytes once, and the settings will persist until the next user change ...

Page 40

... In these situations, two-byte mode should be used to access the E buffer. In this mode, a read will cause the CS8415A to output two bytes from its control port. The first byte out will represent the A channel status data, and the 2nd byte will represent the B channel status data. ...

Page 41

... The nominal center sample rate is the sample rate that the PLL first locks onto upon application of an AES3 data stream or after enabling the CS8415A clocks by setting the RUN control bit. If the 12.5% sample rate limit is exceeded, the PLL will return to its wide lock range mode and re-acquire a new nominal center sample rate ...

Page 42

... FILT and the other three capacitors are in an 0805 FILT 1000 C pF RIP C .1µF FLT Figure 19. Recommended Layout Example CS8415A Figure 5 on page 11 shows the rec- Table Table X7R dielectric is preferred. Avoid ca- DS470F4 6, ...

Page 43

... A1 to revision A2, unless the part is used in an application that is required to pass the AES3 or IEC60958-4 specification for receiver jitter tolerance (see 15.3.1 Identifying the Part Revision The first line of the part marking on the package indicates the part number and package type (CS8415A- xx). Table 4 shows a list of part revisions and their corresponding second line part marking, which indi- cates what revision the part is ...

Page 44

... Jitter Tolerance Shown in Figure 20 is the Receiver Jitter Tolerance template as illustrated in the AES3 and IEC60958-4 specification. CS8415A parts used with the appropriate external PLL component values (as noted in Table 6) have been tested to pass this template. 44 Figure 20. Jitter Tolerance Template CS8415A DS470F4 ...

Page 45

... Jitter Attenuation Shown in Figure 21, Figure sions of the CS8415A when used with the appropriate external PLL component values (as noted in Table 6). The AES3 and IEC60958-4 specifications do not have allowances for locking to sample rates less than 32 kHz. These specifications state a maximum jitter gain or peaking − ...

Page 46

... AC registered trademark of Dolby Laboratories Liscencing, Inc. 46 Changes “Appendix C: PLL Filter” on page 41 Figure 6 on page 14. Figure 6 on page 14 page 13. 21. 27. “Ordering Information” on page www.cirrus.com CS8415A to include information from errata and text reference to page 22. “Control Port Register Bit Defini- page 24 and 2. DS470F4 ...