MAX9421 Maxim, MAX9421 Datasheet - Page 6

MAX9421

Manufacturer Part Number

MAX9421

Description

The MAX9420-MAX9423 are extremely fast, low-skew quad LVECL-to-LVPECL translators designed for high-speed signal and clock driver applications

Manufacturer

Maxim

Datasheet

1.MAX9420.pdf

(13 pages)

The MAX9420–MAX9423 are extremely fast, low-skew

quad LVECL-to-LVPECL translators designed for high-

speed signal and clock driver applications. The

devices feature ultra-low propagation delay of 336ps

and channel-to-channel skew of 17ps.

The four channels can be operated synchronously with

an external clock, or in asynchronous mode, deter-

mined by the state of the SEL input. An enable input

provides the ability to force all the outputs to a differen-

tial low state.

These devices operate with a negative supply voltage

of -2.0V to -3.6V, compatible with LVECL input signals.

The positive supply range is 2.375V to 3.6V for differen-

tial LVPECL output signals.

A variety of input and output terminations are offered

for maximum design flexibility. The MAX9420 has open

inputs and open-emitter outputs. The MAX9421 has

open inputs and 50Ω series outputs. The MAX9422 has

100Ω differential input impedance and open-emitter

outputs. The MAX9423 has 100Ω differential input

impedance and 50Ω series outputs.

For interfacing to differential LVECL input levels, the

V

range is from 2.375V to 3.6V, compatible with LVPECL

logic. Output levels are referenced to V

The MAX9420/MAX9421 have open inputs and require

external termination. The MAX9422/MAX9423 have inte-

grated 100Ω differential input termination resistors from

IN_ to IN_, reducing external component count.

Quad Differential LVECL-to-LVPECL Translators

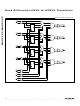

Figure 1. Input and Output Voltage Definitions

6

EE

_______________________________________________________________________________________

range is -2.0V to -3.6V with GND = 0. The V

GND

V

EE

V

V

ID

ID

Detailed Description

INPUT VOLTAGE DEFINITION

Supply Voltages

Data Inputs

V

V

CC

ID

ID

= 0

= 0

.

V

V

V

V

CC

IHD

ILD

IHD

ILD

(MAX)

(MIN)

(MAX)

(MIN)

The MAX9421/MAX9423 have internal 50Ω series out-

put termination resistors and 8mA internal pulldown

current sources. Using integrated resistors reduces

external component count.

The MAX9420/MAX9422 have open-emitter outputs. An

external termination is required. See the Output

Termination section.

Setting EN = high and EN = low enables the device.

Setting EN = low and EN = high forces the outputs to a

differential low. All changes on CLK, SEL, and IN_ are

ignored.

Setting SEL = high and SEL = low enables the four

channels to operate independently as LVECL-to-

LVPECL translators. The CLK signal is ignored in this

mode. In asynchronous mode, the CLK signal should

be set to either logic low or high state to minimize noise

coupling.

Setting SEL = low and SEL = high enables all four

channels to operate in synchronized mode. In this

mode, buffered inputs are clocked into flip-flops simul-

taneously on the rising edge of the differential clock

input (CLK and CLK).

The maximum signal magnitude of all the differential

inputs is 3.0V.

V

OH

- V

OL

OUTPUT VOLTAGE DEFINITION

Differential Signal Input Limit

Asynchronous Operation

Synchronous Operation

V

OCM

V

V

OH

OL

V

GND

CC

Outputs

Enable