MAX9421 Maxim, MAX9421 Datasheet - Page 8

MAX9421

Manufacturer Part Number

MAX9421

Description

The MAX9420-MAX9423 are extremely fast, low-skew quad LVECL-to-LVPECL translators designed for high-speed signal and clock driver applications

Manufacturer

Maxim

Datasheet

1.MAX9420.pdf

(13 pages)

Quad Differential LVECL-to-LVPECL Translators

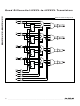

Figure 4. CLK-to-OUT Propagation Delay Timing Diagram

Unused inputs should be biased or driven as shown in

Figure 5. This avoids noise coupling that might cause

toggling at the unused outputs.

Terminate open-emitter outputs (MAX9420/MAX9422)

through 50Ω to V

termination. Terminate outputs using identical termina-

tion on each for the lowest output-to-output skew. When

a single-ended signal is taken from a differential output,

terminate both outputs. For example, if OUT_ is used as

a single-ended output, terminate both OUT_ and OUT_.

Ensure that the output currents do not exceed the cur-

rent limits as specified in the Absolute Maximum

Ratings table. Under all operating conditions, the

device’s total thermal limits should be observed.

Adequate power-supply bypassing is necessary to

maximize the performance and noise immunity. Bypass

V

face-mount ceramic 0.1µF and 0.01µF capacitors in

parallel as close to the device as possible, with the

0.01µF capacitor closest to the device pins. Use multi-

8

CC

_______________________________________________________________________________________

to GND and V

OUT_

OUT_

Applications Information

CLK

CLK

IN_

IN_

CC

EE

- 2V or use an equivalent Thevenin

to GND with high-frequency sur-

Power-Supply Bypassing

Output Termination

t

H

t

PLH2

Input Bias

t

S

V

IHD

V

- V

IHD

ILD

- V

ple parallel vias for ground-plane connection to mini-

mize inductance.

Input and output trace characteristics affect the perfor-

mance of the MAX9420–MAX9423. Connect each of the

inputs and outputs to a 50Ω characteristic impedance

trace. Avoid discontinuities in differential impedance

and maximize common-mode noise immunity by main-

taining the distance between differential traces and

avoid sharp corners. Minimize the number of vias to

prevent impedance discontinuities. Reduce the reflec-

tions by maintaining 50Ω characteristic impedance

through connectors and across cables. Minimize skew

by matching the electrical length of the traces.

TRANSISTOR COUNT: 927

PROCESS: Bipolar

ILD

V

OH

- V

OL

t

H

t

PHL2

Chip Information

Circuit Board Traces

SEL = LOW

EN = HIGH