WM8978_06 Wolfson Microelectronics Ltd., WM8978_06 Datasheet - Page 78

WM8978_06

Manufacturer Part Number

WM8978_06

Description

Stereo Codec With Speaker Driver

Manufacturer

Wolfson Microelectronics Ltd.

Datasheet

1.WM8978_06.pdf

(119 pages)

- Current page: 78 of 119

- Download datasheet (2Mb)

WM8978

w

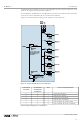

Table 56 Audio Interface Control

Note: Right Justified Mode will only operate with a maximum of 24 bits. If 32-bit mode is selected,

the device will operate in 24-bit mode.

AUDIO INTERFACE CONTROL

The register bits controlling audio format, word length and master / slave mode are summarised

below. The audio interfaces can be controlled individually.

Register bit MS selects audio interface operation in master or slave mode. In Master mode BCLK,

and LRC are outputs. The frequency of BCLK in master mode are controlled with BCLKDIV. These

are divided down versions of master clock. .

R4

Audio

Interface

Control

REGISTER

ADDRESS

0

1

2

4:3

6:5

7

8

BIT

MONO

ADCLRSWAP

DACLRSWAP

FMT

WL

LRP

BCP

LABEL

0

0

0

10

10

DEFAULT

Selects between stereo and mono

device operation:

0=Stereo device operation

1=Mono device operation. Data appears

in ‘left’ phase of LRC

Controls whether ADC data appears in

‘right’ or ‘left’ phases of LRC clock:

0=ADC data appear in ‘left’ phase of

LRC

1=ADC data appears in ‘right’ phase of

LRC

Controls whether DAC data appears in

‘right’ or ‘left’ phases of LRC clock:

0=DAC data appear in ‘left’ phase of

LRC

1=DAC data appears in ‘right’ phase of

LRC

Audio interface Data Format Select:

00=Right Justified

01=Left Justified

10=I

11= DSP/PCM mode

Word length

00=16 bits

01=20 bits

10=24 bits

11=32 bits (see note)

LRC clock polarity

0=normal

1=inverted

BCLK polarity

0=normal

1=inverted

2

S format

DESCRIPTION

PP Rev 3.0 May 2006

Pre-Production

78

Related parts for WM8978_06

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

The WM8978 is a low power, high quality stereo codec designed for portable applications such as Digital still camera or Digital Camcorde

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

Specifications: Manufacturer: Wolfson Microelectronics ; Product Category: ADC (A/D Converters) ; RoHS: Details ; Number of Converters: 1 ; Number of ADC Inputs: 1 ; Conversion Rate: 6 MSPs ; Resolution: 16 bit ; Input Type: Voltage ; Interface

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

WM8192 : 16-BIT, 6MSPS Cis/ccd Image Digitiser With Multiplexed Output

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

The WM8976 is a low power, high quality stereo codec designed for portable applications such as Digital still camera or Digital Camcorde

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

WM8141 : 12-BIT 6MSPS Cis/ccd Analogue Front End/digitiser

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

WM8143 : 10 or 12-BIT, 4MSPS Analogue Front End For CCD Image Sensors

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

WM8143 : 10 or 12-BIT, 4MSPS Analogue Front End For CCD Image Sensors

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

Integrated 10-bit Data Acquisition System For Imaging Applications

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

12-bit ( 8+4-bit ) Linear Sensor Image Processor

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet:

Part Number:

Description:

WM8148 : 12-BIT/12 MSPS Ccd/cis Analogue Front End/digitiser

Manufacturer:

Wolfson Microelectronics Ltd.

Datasheet: