LTC2928 Linear Technology, LTC2928 Datasheet - Page 13

LTC2928

Manufacturer Part Number

LTC2928

Description

Multichannel Power Supply Sequencer and Supervisor

Manufacturer

Linear Technology

Datasheet

1.LTC2928.pdf

(32 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

LTC2928CG

Manufacturer:

LINEAR/凌特

Quantity:

20 000

Part Number:

LTC2928CG#PBF

Manufacturer:

LINEAR/凌特

Quantity:

20 000

Part Number:

LTC2928CG#TRPBF

Manufacturer:

LINEAR/凌特

Quantity:

20 000

Part Number:

LTC2928CUHF#PBF

Manufacturer:

LINEAR/凌特

Quantity:

20 000

Company:

Part Number:

LTC2928CUHF#PBF/IU

Manufacturer:

LT

Quantity:

82

Part Number:

LTC2928CUHF#TRPBF

Manufacturer:

LINEAR/凌特

Quantity:

20 000

Company:

Part Number:

LTC2928IG#PBF

Manufacturer:

LT

Quantity:

23

OPERATIO

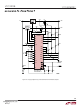

At the beginning of the sequence-up phase, a current

source begins to charge the STMR capacitance. When the

sequence timer has expired the CAS pin pulls low. At this

time, any enable (EN) scheduled (using the RT inputs) for

“time position 1” pulls high, allowing a supply (or supplies)

to be turned on. The CAS pin is held low until all monitored

inputs in the current time position exceed their selected

sequencing-up threshold (25μs minimum).

Once all supply monitor inputs cross their sequencing-up

threshold, or if no enable was selected for the current time

position, the CAS pin is allowed to pull high. The STMR

capacitor begins to charge again, moving the system to

“time position 2”. This process repeats until the system

is clocked through “time position 8”.

During the sequence-up phase, supply monitor inputs are

expected to cross their sequence-up threshold (which may

be different from their undervoltage threshold). Any supply

monitor input failing to cross its sequence-up threshold

will stall the process and a sequence-up fault is gener-

ated (if the power-good timer is active). The power-good

timer starts with the first enable output to go high and is

cleared when the last supply monitor input reaches its

undervoltage threshold. Any supply monitor input failing

to cross its sequence-up threshold before the power-

good timer expires also generates a sequence-up fault. A

sequence-up fault pulls F L T and all supply enable outputs

(EN) low. Use a single capacitor from PTMR to ground to

select the power good time. To disable the power good

timer, simply tie PTMR to ground.

Each comparator switches to its undervoltage threshold

when the respective supply monitor input crosses its

sequence-up threshold. The comparator outputs are

allowed to pull high after the LTC2928 clocks through

time position 8.

After a system fault, fault information is latched to the

CMP outputs. Read the CMP outputs to obtain the fault

type (internally generated sequence-fault, reset-fault, com-

mand-fault or an externally generated fault) and the fault

channel (if any). For more details refer to the discussion

on system faults later in this document.

After the system has clocked through “time position 8”,

the last LTC2928 (defined by a 2.4k to 5.1k pull-up resistor

on D O N E ) pulls down on D O N E .

U

Supply Monitor Phase

Once all supply monitor inputs have crossed their

sequence-up thresholds, the LTC2928 enters its supply

monitor phase. As referred to earlier, the comparators

switch to their highly accurate undervoltage thresholds

after crossing their sequence-up threshold. The monitor

thresholds maintain 1.5% accuracy over temperature.

R S T pulls high after all supply monitor inputs (V1 to V4)

have been above their undervoltage threshold for the

selected reset delay time. The reset delay is set with a

capacitor attached between RTMR and ground.

The supply monitor comparators will filter out minor

glitches coupled to their inputs. If any supply falls below

threshold with sufficient magnitude and duration, the

R S T line pulls low. The reset timer starts once all inputs

return above threshold.

The LTC2928 can be configured to issue a fault if R S T

pulls low due to an undervoltage event (see master/slave

configuration table in Applications Information). Upon a

R S T fault, F L T and the enable outputs pull low. Use the

fault report capability to determine which input was below

threshold. For more details refer to the discussion on

system faults later in this document.

The reset disable input (RDIS) may be pulled high or low

to force R S T high regardless of voltage monitor level. This

feature is useful during voltage margining tests.

Sequence-Down Phase

The sequence-down phase is initiated by pulling the ON

input below 0.97V. This action pulls R S T low immediately.

The comparator thresholds (and REF for negative supplies)

are moved to their selected sequence-down thresholds.

Beginning with any supplies in “time position 8”, the enable

outputs are sequenced-down by pulling enable low in the

reverse order of sequence-up (last on, first off).

During the sequence-down phase, supply monitor

inputs are expected to cross their sequence-down

thresold (which may be different from their undervoltage

threshold) within the selected power good time. Any

supply monitor input failing to cross its sequence-down

threshold will stall the process and a sequence-down fault is

generated (if the power-good timer is active).The power-

www.DataSheet4U.com

LTC2928

13

2928f