ics87951i-147 Integrated Device Technology, ics87951i-147 Datasheet

ics87951i-147

Related parts for ics87951i-147

ics87951i-147 Summary of contents

Page 1

... LOW SKEW, 1-TO-9 DIFFERENTIAL-TO- LVCMOS ZERO DELAY BUFFER G D ENERAL ESCRIPTION The ICS87951I-147 is a low voltage, low skew to-9 Differential-to-LVCMOS/LVTTL Zero Delay HiPerClockS™ Buffer and a member of the HiPerClockS™ family of High Performance Clock Solutions from ICS. The ICS87951I-147 has two selectable clock in- puts ...

Page 2

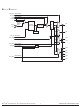

... Internal Pulldown MR/nOE Internal Pulldown DIV_SELD IDT ™ / ICS ™ DIFFERENTIAL-TO-LVCMOS ZERO DELAY BUFFER 1 0 PHASE VCO DETECTOR 250-500MHz LPF POWER-ON RESET 2 ÷ ÷ ÷ QC0 0 1 QC1 QD0 QD1 0 QD2 1 QD3 QD4 ICS87951I-147 REV A JUNE 21, 2006 ...

Page 3

... ICS87951I-147 REV A JUNE 21, 2006 ...

Page 4

... ICS87951I-147 REV A JUNE 21, 2006 ...

Page 5

... ICS87951I-147 REV A JUNE 21, 2006 ...

Page 6

... ICS87951I-147 REV A JUNE 21, 2006 µ ...

Page 7

... ICS87951I-147 REV A JUNE 21, 2006 ...

Page 8

... Phase Jitter mean t (Ø) = Static Phase Offset mean (where t (Ø) is any random sample, and t (Ø) of the sampled cycles measured on controlled edges ITTER AND TATIC HASE FFSET ICS87951I-147 REV A JUNE 21, 2006 SCOPE Qx 80% 20 the average mean ...

Page 9

... UPPLY ILTERING ECHNIQUES As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. The ICS87951I-147 provides separate power supplies to isolate any high switching noise from the outputs to the internal PLL. V should be individually connected to the power supply plane through vias, and bypass capacitors should be used for each pin ...

Page 10

... Ohm nCLK HiPerClockS LVPECL Input 3B CLK/nCLK LOCK 3.3V LVPECL D RIVER 3. Ohm LVDS_Driv er R1 100 Ohm 3D CLK/nCLK LOCK 3.3V LVDS D RIVER ICS87951I-147 REV A JUNE 21, 2006 D NPUT RIVEN BY 3.3V CLK nCLK Receiv er D NPUT RIVEN BY ...

Page 11

... Multi-Layer PCB, JEDEC Standard Test Boards NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs RANSISTOR OUNT The transistor count for ICS87951I-147 is: 2674 Pin compatible with the MPC951 IDT ™ / ICS ™ DIFFERENTIAL-TO-LVCMOS ZERO DELAY BUFFER ...

Page 12

... ° ICS87951I-147 REV A JUNE 21, 2006 ...

Page 13

... ICS87951I-147 REV A JUNE 21, 2006 ° ° ° ° ° ° ° ...

Page 14

... ICS87951I-147 REV A JUNE 21, 2006 ...

Page 15

... ICS87951I-147 xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx LOW SKEW, 1-TO-9, DIFFERENTIAL-TO-LVCMOS ZERO DELAY BUFFER xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx Innovate with IDT and accelerate your future networks. Contact: www.IDT.com For Sales For Tech Support 800-345-7015 netcom@idt.com 408-284-8200 480-763-2056 Fax: 408-284-2775 Corporate Headquarters Asia Pacific and Japan Integrated Device Technology, Inc. ...