ics87952i-147 Integrated Device Technology, ics87952i-147 Datasheet

ics87952i-147

Related parts for ics87952i-147

ics87952i-147 Summary of contents

Page 1

... Low Skew, 1-to-11 LVCMOS/LVTTL Clock Multiplier/Zero Delay Buffer G D ENERAL ESCRIPTION The ICS87952I-147 is a low voltage, low skew IC S LVCMOS/LVTTL Clock Generator and a member of HiPerClockS™ the HiPerClockS™ family of High Performance Clock Solutions from IDT. With output frequencies up to 180MHz, the ICS87952I-147 is targeted for high performance clock applications ...

Page 2

... ICS87952I-147 Data Sheet ABLE IN ESCRIPTIONS ...

Page 3

... ICS87952I-147 Data Sheet BSOLUTE AXIMUM ATINGS Supply Voltage Inputs Outputs Package Thermal Impedance, θ JA Storage Temperature, T STG T 4A ABLE OWER UPPLY HARACTERISTICS ...

Page 4

... ICS87952I-147 Data Sheet ABLE HARACTERISTICS ...

Page 5

... ICS87952I-147 Data Sheet P ARAMETER 1.65V± DDO LVCMOS GND -1.65V±5% 3. UTPUT OAD EST IRCUIT QAx QBx, DDO DDO 2 QCx ➤ ➤ ➤ tcycle n tjit(cc) = tcycle n – tcycle n+1 1000 Cycles YCLE TO YCLE ITTER REF_CLK V DDO ...

Page 6

... ILTERING ECHNIQUES As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. The ICS87952I-147 provides separate power supplies to isolate any high switching noise from the outputs to the internal PLL ...

Page 7

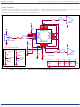

... ICS87952I-147 Data Sheet L G AYOUT UIDELINE The schematic of the ICS87952I-147 layout example is shown in Figure 2A. This layout example is used as a general guideline. The layout in the actual system will depend on the selected com- VDD Ohm R3 43 Driv er_LVCMOS Logic Input Pin Examples ...

Page 8

... ICS87952I-147 Data Sheet The following component footprints are used in this layout example: All the resistors and capacitors are size 0603 OWER AND ROUNDING Place the decoupling capacitors as close as possible to the power pins. If space allows, placement of the decoupling capacitor on the component side is preferred. This can reduce unwanted inductance between the decoupling capacitor and the power pin caused by the via ...

Page 9

... VS IR LOW ABLE FOR JA Multi-Layer PCB, JEDEC Standard Test Boards T C RANSISTOR OUNT The transistor count for ICS87952I-147 is: 2882 Compatible with MPC952, MPC9352, MPC93R52 ICS87952AYI-147 REVISION C AUGUST 4, 2009 LOW SKEW, 1-TO-11 LVCMOS/LVTTL CLOCK MULTIPLIER/ZERO DELAY BUFFER R I ELIABILITY NFORMATION 32 L LQFP EAD θ ...

Page 10

... ICS87952I-147 Data Sheet ACKAGE UTLINE UFFIX FOR T ABLE Reference Document: JEDEC Publication 95, MS-026 ICS87952AYI-147 REVISION C AUGUST 4, 2009 LOW SKEW, 1-TO-11 LVCMOS/LVTTL CLOCK MULTIPLIER/ZERO DELAY BUFFER LQFP EAD ACKAGE IMENSIONS ...

Page 11

... ICS87952I-147 Data Sheet ABLE RDERING NFORMATION ...

Page 12

... ICS87952I-147 Data Sheet ICS87952AYI-147 REVISION C AUGUST 4, 2009 LOW SKEW, 1-TO-11 LVCMOS/LVTTL CLOCK MULTIPLIER/ZERO DELAY BUFFER ...

Page 13

... ICS87952I-147 Data Sheet www.IDT.com 6024 Silver Creek Valley Road Sales San Jose, CA 95138 800-345-7015 (inside USA) +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com/go/contactIDT DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT’s sole discretion. All information in this document, including descriptions of product features and performace, is subject to change without notice ...