dp8421a National Semiconductor Corporation, dp8421a Datasheet - Page 49

dp8421a

Manufacturer Part Number

dp8421a

Description

Microcmos Programmable 256k/1m/4m Dynamic Ram Controller/drivers

Manufacturer

National Semiconductor Corporation

Datasheet

1.DP8421A.pdf

(58 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

dp8421aTV-25

Manufacturer:

NSC

Quantity:

12 388

Part Number:

dp8421aTV-25

Manufacturer:

NS/国半

Quantity:

20 000

Company:

Part Number:

dp8421aTVX-25

Manufacturer:

Texas Instruments

Quantity:

10 000

Company:

Part Number:

dp8421aV-20

Manufacturer:

NSC

Quantity:

5 510

Company:

Part Number:

dp8421aV-20

Manufacturer:

Texas Instruments

Quantity:

10 000

Part Number:

dp8421aV-20

Manufacturer:

NS/国半

Quantity:

20 000

Company:

Part Number:

dp8421aV-25

Manufacturer:

Texas Instruments

Quantity:

10 000

Part Number:

dp8421aV-25

Manufacturer:

NS/国半

Quantity:

20 000

Company:

Part Number:

dp8421aV25

Manufacturer:

NSC

Quantity:

12 388

Company:

Part Number:

dp8421aVX-25

Manufacturer:

MOT

Quantity:

29

300

301a

301b

302

303

304

305

306

307

308a

308b

308c

308d

309

310

311

312

313

314

315

316

Number

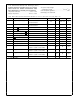

13 0 AC Timing Parameters

Unless otherwise stated V

per bank including trace capacitance (Note 2)

Two different loads are specified

C

C

L

L

e

e

50 pF loads on all outputs except

150 pF loads on Q0 – 8 9 10 and WE or

tSCSCK

tSALECKNL

tSALECKL

tWALE

tSBADDCK

tSADDCK

tHASRCB

tSRCBAS

tPCKRL

tPCKCL0

tPCKCL1

tPCKCL2

tPCKCL3

tHCKALE

tSWINCK

tPCSWL

tPCSWH

tPCLKDL1

tPALEWL

tPCKCV0

Symbol

CS Asserted to CLK High

ALE Asserted Setup to CLK High

Not Using On-Chip Latches or

if Using On-Chip Latches and

B0 B1 Are Constant Only 1 Bank

ALE Asserted Setup to CLK High

if Using On-Chip Latches if B0 B1

Can Change More Than One Bank

ALE Pulse Width

Bank Address Valid Setup to CLK High

Row Column Valid Setup to

CLK High to Guarantee

tASR

Row Column Bank Address

Held from ALE Negated

(Using On-Chip Latches)

Row Column Bank Address

Setup to ALE Negated

(Using On-Chip Latches)

CLK High to RAS Asserted

CLK High to CAS Asserted

(t

CLK High to CAS Asserted

(t

CLK High to CAS Asserted

(t

CLK High to CAS Asserted

(t

ALE Negated Hold from CLK High

WIN Asserted Setup to CLK High

to Guarantee CAS is Delayed

CS Asserted to WAIT Asserted

CS Negated to WAIT Negated

CLK High to DTACK Asserted

(Programmed as DTACK0)

ALE Asserted to WAIT Asserted

(CS is Already Asserted)

AREQ Negated to CLK High That Starts

Access RAS to Guarantee tASR

(Non-Interleaved Mode Only)

CLK High to Column

Address Valid

(t

RAH

RAH

RAH

RAH

RAH

CC

e

e

e

e

e

e

e

Parameter Description

5 0V

0 ns

15 ns t

15 ns t

25 ns t

25 ns t

15 ns t

Mode 0 Access

g

10% 0 C

ASC

ASC

ASC

ASC

ASC

e

e

e

e

e

(Continued)

0 ns)

10 ns)

0 ns)

10 ns)

0 ns)

k

T

A k

e

70 C the output load capacitance is typical for 4 banks of 18 DRAMs

0 ns

49

b

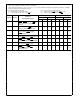

Min

C

C

C

14

16

29

18

20

11

10

41

3

0

21

H

H

H

8420A 21A 22A-20

e

e

e

C

L

50 pF loads on all outputs except

125 pF loads on RAS0 – 3 and CAS0 – 3 and

380 pF loads on Q0 – 8 9 10 and WE

Max

101

27

81

91

91

26

30

40

35

78

b

Min

14

16

29

18

20

15

10

45

3

0

21

C

H

Max

109

32

89

99

99

26

30

40

35

87

b

Min

13

15

29

13

18

11

34

8

2

0

16

8420A 21A 22A-25

C

L

Max

22

72

82

82

92

22

25

32

29

66

b

Min

13

15

29

13

18

16

39

8

2

0

16

C

H

Max

26

79

89

89

99

22

25

32

29

75