at89c55-12qi ATMEL Corporation, at89c55-12qi Datasheet

at89c55-12qi

Related parts for at89c55-12qi

at89c55-12qi Summary of contents

Page 1

... The on-chip Flash allows the program memory to be reprogrammed in-system conventional nonvolatile memory programmer. By combining a versatile 8 bit CPU with Flash on a monolithic chip, the Atmel AT89C55 is a powerful microcomputer which provides a highly flexible and cost effective solution to many embedded control applications. Pin Configurations ...

Page 2

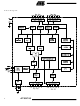

... Block Diagram AT89C55 2 ...

Page 3

... As inputs, Port 3 pins that are externally being pulled low will source current (I ) because of the pullups. IL Port 3 also serves the functions of various special features of the AT89C55, as shown in the following table. Alternate Functions Port Pin P3.0 RXD (serial input port) P3.1 TXD (serial output port) P3 ...

Page 4

... PSEN Program Store Enable is the read strobe to external pro- gram memory. When the AT89C55 is executing code from external pro- gram memory, PSEN is activated twice each machine cy- cle, except that two PSEN activations are skipped during each access to external data memory. ...

Page 5

... Table 1. AT89C55 SFR Map and Reset Values 0F8H B 0F0H 00000000 0E8H ACC 0E0H 00000000 0D8H PSW 0D0H 00000000 T2CON T2MOD 0C8H 00000000 XXXXXX00 0C0H IP 0B8H XX000000 P3 0B0H 11111111 IE 0A8H 0X000000 P2 0A0H 11111111 SCON SBUF 98H 00000000 XXXXXXXX P1 90H 11111111 TCON TMOD ...

Page 6

... Capture/Reload select. CP/RL2 = 1 causes captures to occur on negative transitions at T2EX if EXEN2 = 1. CP/RL2 = 0 causes automatic reloads to occur when Timer 2 overflows or negative transitions occur at T2EX when EXEN2 = 1. When either RCLK or TCLK = 1, this bit is ignored and the timer is forced to auto-reload on Timer 2 overflow. AT89C55 6 RCLK TCLK ...

Page 7

... Timer 0 and 1 Timer 0 and Timer 1 in the AT89C55 operate the same way as Timer 0 and Timer 1 in the AT89C51 and AT89C52. For further information, see the Microcontroller Data Book, section titled, "Timer/Counters." Timer 2 Timer bit Timer/Counter that can operate as either a timer or an event counter ...

Page 8

... T20E Timer 2 Output Enable bit. DCEN When set, this bit allows Timer configured as an up/down counter. AT89C55 8 RCAP2H and RCAP2L to be reloaded into the timer regis- ters, TH2 and TL2, respectively. A logic 0 at T2EX makes Timer 2 count down. The timer underflows when TH2 and TL2 equal the values stored in RCAP2H and RCAP2L ...

Page 9

... Figure 3. Timer 2 Auto Reload Mode (DCEN = 1) Figure 4. Timer 2 in Baud Rate Generator Mode AT89C55 9 ...

Page 10

... As a baud rate generator, however, it increments every state time (at 1/2 the oscilla- tor frequency). The baud rate formula is given below. Figure 5. Timer 2 in Clock-Out Mode AT89C55 10 Modes 1 and 3 Baud Rate where (RCAP2H, RCAP2L) is the content of RCAP2H and RCAP2L taken bit unsigned integer ...

Page 11

... RCAP2H and RCAP2L. UART The UART in the AT89C55 operates the same way as the UART in the AT89C51 and AT89C52. For further informa- tion, see the Microcontroller Data Book, section titled, "Se- rial Interface." ...

Page 12

... Status of External Pins During Idle and Power Down Mode Program Memory Idle Internal Idle External Power Down Internal Power Down External AT89C55 12 Figure 7. Oscillator Connections Notes: C1 Figure 8. External Clock Drive Configuration ALE PSEN PORT0 1 1 Data 1 ...

Page 13

... Program Memory Lock Bits The AT89C55 has three lock bits that can be left unpro- grammed (U) or can be programmed (P) to obtain the ad- ditional features listed in the following table. Lock Bit Protection Modes ...

Page 14

... Programming the Flash (Continued) Data Polling: The AT89C55 features Data Polling to indi- cate the end of a write cycle. During a write cycle, an at- tempted read of the last byte written will result in the com- plement of the written data on PO.7. Once the write cycle has been completed, true data is valid on all outputs, and the next cycle may begin ...

Page 15

... V = 12V should be used enable programming. ALE/ EA/ PSEN V PROG PP (1) L H/12V H/12V L H/12V L H/12V (2) L H/12V Chip Erase requires PROG pulse. AT89C55 P2.6 P2 ...

Page 16

... Address to Data Valid AVQV t ENABLE Low to Data Valid ELQV t Data Float After ENABLE EHQZ t PROG High to BUSY Low GHBL t Byte Write Cycle Time WC Note: 1. Only used in 12-volt programming mode. AT89C55 16 Min 11.5 4 48t CLCL 48t CLCL 48t CLCL 48t CLCL 48t PP CLCL ...

Page 17

... Flash Programming and Verification Waveforms - High Voltage Mode Flash Programming and Verification Waveforms - Low V Mode (5-volt Programming) AT89C55 Voltage PP 17 ...

Page 18

... OL Maximum I per 8 bit port: Port 0: 26 mA, OL Ports AT89C55 18 *NOTICE: Stresses beyond those listed under “Absolute Maxi- mum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indi- cated in the operational sections of this specification is not implied ...

Page 19

... Address Low AVWL t Data Valid to WR Transition QVWX t Data Valid to WR High QVWH t Data Hold After WR WHQX t RD Low to Address Float RLAZ High to ALE High WHLH AT89C55 12 MHz Oscillator Variable Oscillator Min Max Min 0 127 CLCL CLCL 48 t ...

Page 20

... External Program Memory Read Cycle External Data Memory Read Cycle AT89C55 20 ...

Page 21

... External Data Memory Cycle External Clock Drive Waveforms External Clock Drive Symbol Parameter 1/t Oscillator Frequency CLCL t Clock Period CLCL t High Time CHCX t Low Time CLCX t Rise Time CLCH t Fall Time CHCL AT89C55 Min Max Units MHz ...

Page 22

... Note Inputs during testing are driven at V for a logic 1 and 0.45V for a logic 0. Timing meas- urements are made at V min. for a logic 1 and IH V max. for a logic 0. IL AT89C55 22 = 5.0V 20% and Load Capacitance = 80 pF MHz Osc Min Max 1.0 700 ...

Page 23

... AT89C55 23 ...

Page 24

... Ordering Information Speed Power Ordering Code (MHz) Supply 12 5V 20% AT89C55-12AC AT89C55-12JC AT89C55-12PC AT89C55-12QC AT89C55-12AI AT89C55-12JI AT89C55-12PI AT89C55-12QI AT89C55-12AA AT89C55-12JA AT89C55-12PA AT89C55-12QA 16 5V 20% AT89C55-16AA AT89C55-16JA AT89C55-16PA AT89C55-16QA 24 5V 20% AT89C55-24AC AT89C55-24JC AT89C55-24PC AT89C55-24QC AT89C55-24AI AT89C55-24JI AT89C55-24PI AT89C55-24QI 33 5V 10% AT89C55-33AC AT89C55-33JC AT89C55-33PC AT89C55-33QC 44A ...