lm5020sdx-2 National Semiconductor Corporation, lm5020sdx-2 Datasheet - Page 9

lm5020sdx-2

Manufacturer Part Number

lm5020sdx-2

Description

100v Current Mode Pwm Controller

Manufacturer

National Semiconductor Corporation

Datasheet

1.LM5020SDX-2.pdf

(13 pages)

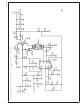

Oscillator and Sync Capability

A single external resistor connected between the RT and

GND pins sets the LM5020 oscillator frequency. Internal to

the LM5020-2 device (50% duty cycle limited option) is an

oscillator divide by two circuit. This divide by two circuit

creates an exact 50% duty cycle pulse which is used inter-

nally to create a precise 50% duty cycle limit function. Be-

cause of this, the internal oscillator actually operates at twice

the frequency of the output (OUT). For the LM5020-1 device

the oscillator frequency and the operational output frequency

are the same. To set a desired output operational frequency

(F), the RT resistor can be calculated from:

LM5020-1:

LM5020-2:

The LM5020 can also be synchronized to an external clock.

The external clock must have a higher frequency than the

free running oscillator frequency set by the RT resistor. The

clock signal should be capacitively coupled into the RT pin

through a 100pF capacitor. A peak voltage level greater than

3.7 Volts at the RT pin is required for detection of the sync

pulse. The sync pulse width should be set between 15 to

150ns by the external components. The RT resistor is al-

ways required, whether the oscillator is free running or ex-

ternally synchronized. The voltage at the RT pin is internally

regulated at 2 Volts. The RT resistor should be located very

close to the device and connected directly to the pins of the

controller (RT and GND).

PWM Comparator / Slope

Compensation

The PWM comparator compares the current ramp signal

with the loop error voltage derived from the error amplifier

output. The error amplifier output voltage at the COMP pin is

offset by 1.4V and then further attenuated by a 3:1 resistor

divider. The PWM comparator polarity is such that 0 Volts on

the COMP pin will result in a zero duty cycle at the controller

output. For duty cycles greater than 50 percent, current

mode control circuits are subject to sub-harmonic oscillation.

By adding an additional fixed slope voltage ramp signal

9

(slope compensation) to the current sense signal, this oscil-

lation can be avoided. The LM5020-1 integrates this slope

compensation by summing a current ramp generated by the

oscillator with the current sense signal. Additional slope

compensation may be added by increasing the source im-

pedance of the current sense signal. Since the LM5020-2 is

not capable of duty cycles greater than 50%, there is no

slope compensation feature in this device.

Soft Start

The softstart feature allows the power converter to gradually

reach the initial steady state operating point, thereby reduc-

ing start-up stresses and current surges. At power on, after

the V

satisfied, an internal 10µA current source charges an exter-

nal capacitor connected to the SS pin. The capacitor voltage

will ramp up slowly and will limit the COMP pin voltage and

the duty cycle of the output pulses.

Gate Driver and Maximum Duty

Cycle Limit

The LM5020 provides an internal gate driver (OUT), which

can source and sink a peak current of 1 Amp. The LM5020 is

available in two duty cycle limit options. The maximum out-

put duty cycle is typically 80% for the LM5020-1 option and

precisely equal to 50% for the LM5020-2 option. The maxi-

mum duty cycle function for the LM5020-2 is accomplished

with an internal toggle flip-flop which ensures an accurate

duty cycle limit. The internal oscillator frequency of the

LM5020-2 is therefore twice the operating frequency of the

PWM controller (OUT pin).

The 80% maximum duty cycle limit of the LM5020-1 is

determined by the internal oscillator and varies more than

the 50% limit of the LM5020-2. For the LM5020-1 the internal

oscillator frequency and the operational frequency of the

PWM controller are equal.

Thermal Protection

Internal thermal shutdown circuitry is provided to protect the

integrated circuit in the event the maximum junction tem-

perature is exceeded. This feature prevents catastrophic

failures from accidental device overheating. When activated,

typically at 165 degrees Celsius, the controller is forced into

a low power standby state, disabling the output driver and

the bias regulator. After the temperature is reduced (typical

hysteresis = 25˚C) the V

start sequence initiated.

CC

and the line undervoltage lockout thresholds are

CC

regulator is enabled and a soft-

www.national.com