am79c850 Advanced Micro Devices, am79c850 Datasheet - Page 64

am79c850

Manufacturer Part Number

am79c850

Description

Supernet-r 3

Manufacturer

Advanced Micro Devices

Datasheet

1.AM79C850.pdf

(97 pages)

1. The stuck-at 1 (s@1) condition in the mask bits for a

2. The stuck-at 0 (s@0) condition in the mask bits for a

Part #1

a) Write each data entry with all 0’s.

b) Write the comparand register with all 0’s.

c) Perform a match operation—should get an all match

The individual match lines for each entry must be OR’d

together to determine if a match has occurred. The indi-

vidual exact match lines must also be OR’d together to

determine if an exact match has occurred. The pattern

shown in the first line of the table will detect all s@0

faults on the logic that generates each match and exact

line for an entry. It will also check for a s@0 fault on the

final match and exact outputs. The pattern shown in the

second line of the table will check for all s@1 faults aris-

ing from the SAX personality bits and will also detect a

s@1 fault on the final exact output. The pattern shown in

the third line of the table will check for s@1 faults on the

VALID personality bits as well as on the final match and

exact outputs. The final pattern shown in the fourth line

64

comparator can be checked by first writing all mask

bits to 0’s, all data bits to 0’s and the comparand

register to all 1’s. If any single mask bit is s@1, no

match will occur otherwise a match will result as can

be seen from the first line of table 1. To speed the

testing for this condition, all entries can be tested in

parallel if an all match indication is provided. All mask

and data bits are written with 0’s and compared

simultaneously with the comparand. Each entry

should match resulting in the all match condition. If

any mask bit is s@1, the all match condition will not

occur and the fault can be detected.

comparator are tested by the data patterns shown in

the third and fourth lines of table 1. These lines are a

subset of the patterns needed to test the XNOR

faults that are represented by lines 2 through 5 of

table 1. The outputs of the XNOR gates for each bit

are all AND’ed together to form the match output of

the comparator. The following test description will

cover all stuck-at faults for the remainder of the

comparator logic. These tests assume that all mask

bits are written with 1’s and assume the existence of

an all match indication. The test is described in

two parts:

indication.

AMD

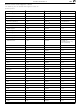

SAX

1

0

1

1

VALID

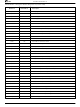

Table 2. Patterns necessary for match and exact indicators

1

1

0

1

SA

1

1

1

0

P R E L I M I N A R Y

SUPERNET 3

MATCH[i]

d) Repeat steps a through c but this time use all 1’s. At

Part #2

a) Write each data entry with all 0’s.

b) Do 48 matches while walking a 1 through a field of 0’s

c) Repeat steps a and b with each data entry being all

Source address exact/inexact logic:

The SRAM portion of this logic, namely the storage for

the SA and SAX personality bits will be tested by the

SRAM tests presented earlier. What remains to be

tested is the logic that generates the source address

match and the source address match exact logic.

The test pattern description that follows does not yet

take into account the impact of the SKIP bit since its use

hasn’t been completely determined as yet. The patterns

also assume the existence of an all match indication as

described earlier. The following table summarizes the

patterns that need to be applied to check each entry

match and exact indicators:

of the table will check for s@1 faults on the SA personal-

ity bits as well as on the final match and exact outputs.

One could argue that the first pattern is not sufficient to

cover all possible s@0 faults in the final OR’ing of the

individual match and exact lines since these faults are

detected on the assumption of the existence of an all

match indication (an all exact indication is also neces-

sary). The all match indicator is used to speed the

testing of the AF since all entries can be written with the

same values. If someone is uncomfortable with this

potential loss in coverage, then an additional 32

patterns are needed that only apply the first pattern of

the table to each entry by itself so that only one entry

1

1

0

0

this point half of the XNOR tests (lines 2 and 5 in

table 1) have been completed and the AND circuitry

has been tested for s@0 faults.

in the comparand register. Since a single bit is in

error for each match, a match condition should never

occur.

1’s and walking a 0 through a field of 1’s in the

comparand. At this point, all the XNOR tests are

completed. This also checks for s@1 faults in the

AND circuitry since all but a single bit match. This

test also tests for the mask bit s@0.

EXACT[i]

1

0

0

0

ALL MATCH?

YES

YES

NO

NO