hy5du561622flfp Hynix Semiconductor, hy5du561622flfp Datasheet

hy5du561622flfp

Related parts for hy5du561622flfp

hy5du561622flfp Summary of contents

Page 1

... DDR SDRAM HY5DU561622F(L)FP This document is a general product description and is subject to change without notice. Hynix Semiconductor does not assume any responsibility for use of circuits described. No patent licenses are implied. Rev. 1.0 /Nov. 2007 1 ...

Page 2

Revision History Revision No. 1.0 Rev. 1.0 /Nov. 2007 History First Version Release HY5DU561622F(L)FP Draft Date Remark Nov. 2007 2 ...

Page 3

DESCRIPTION The HY5DU561622F(L)FP-xxI are a 268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM, ideally suited for the main memory applications which requires large memory density and high bandwidth. This Hynix 256Mb DDR SDRAMs offer fully synchronous operations referenced to both rising ...

Page 4

Column Address Auto Precharge Flag Rev. 1.0 /Nov. 2007 VSSQ DQ15 VSS B DQ14 VDDQ DQ13 C DQ12 VSSQ DQ11 D DQ10 VDDQ DQ9 E DQ8 VSSQ UDQS LDQS F VREF VSS UDM G CK /CK ...

Page 5

PIN DESCRIPTION PIN TYPE CK, /CK Input CKE Input /CS Input BA0, BA1 Input A0 ~ A12 Input /RAS, /CAS, /WE Input DM Input (LDM,UDM) DQS I/O (LDQS,UDQS Supply Supply DDQ SSQ ...

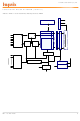

Page 6

FUNCTIONAL BLOCK DIAGRAM (16Mx16) 4Banks x 4Mbit x 16 I/O Double Data Rate Synchronous DRAM CLK /CLK CKE Comman /CS d Decoder /RAS /CAS / Address Buffer max A BA0 BA1 Rev. 1.0 /Nov. 2007 Write Data Register ...

Page 7

SIMPLIFIED COMMAND TRUTH TABLE Command CKEn-1 1,2 Extended Mode Register Set 1,2 Mode Register Set 1 Device Deselect 1 No Operation 1 Bank Active 1 Read 1,3 Read with Autoprecharge 1 Write 1,4 Write with Autoprecharge 1,5 Precharge All Banks ...

Page 8

WRITE MASK TRUTH TABLE Function CKEn-1 1 Data Write 1 Data-In Mask Note: 1. Write Mask command masks burst write data with reference to LDQS/UDQS(Data Strobes) and it is not related with read data. In case of x16 data I/O, ...

Page 9

SIMPLIFIED STATE DIAGRAM lie ...

Page 10

POWER-UP SEQUENCE AND DEVICE INITIALIZATION DDR SDRAMs must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation. Power must first be applied to VDD, then to VDDQ, and finally ...

Page 11

Power-Up Sequence VDD VDDQ tVTD VTT VREF /CLK CLK tIS tIH LVCMOS Low Level CKE CMD NOP DM ADDR A10 BA0, BA1 DQS DQ'S T=200usec Power UP VDD and CK stable Rev. 1.0 /Nov. 2007 PRE EMRS MRS NOP PRE ...

Page 12

MODE REGISTER SET (MRS) The mode register is used to store the various operating modes such as /CAS latency, addressing mode, burst length, burst type, test mode, DLL reset. The mode register is programed via MRS command. This command is ...

Page 13

BURST DEFINITION Burst Length Starting Address (A2,A1,A0 BURST LENGTH & TYPE Read and write accesses to the DDR SDRAM are burst oriented, with the burst length being programmable. The burst length determines the maximum number of column ...

Page 14

CAS LATENCY The Read latency or CAS latency is the delay in clock cycles between the registration of a Read command and the availability of the first burst of output data. The latency can be programmed 2 or 2.5 clocks ...

Page 15

EXTENDED MODE REGISTER SET (EMRS) The Extended Mode Register controls functions beyond those controlled by the Mode Register; these additional func- tions include DLL enable/disable, output driver strength selection(optional). These functions are controlled via the bits shown below. The Extended ...

Page 16

ABSOLUTE MAXIMUM RATINGS Parameter Operating Temperature (Ambient) Storage Temperature Voltage on V relative Voltage on V relative to V DDQ SS Voltage on inputs relative Voltage on I/O pins relative ...

Page 17

IDD SPECIFICATION AND CONDITIONS Test Conditions Operating Current: One bank; Active - Precharge; tRC=tRC(min); tCK=tCK(min); DQ,DM and DQS inputs changing twice per clock cycle; address and control inputs changing once per clock cycle Operating Current: One bank; Active - Read ...

Page 18

IDD Specification 16Mx16 Parameter Operating Current Operating Current Precharge Power Down Standby Current Idle Standby Current Active Power Down Standby Current Active Standby Current Operating Current Operating Current Auto Refresh Current Normal Self Refresh Current Low Power Operating Current - ...

Page 19

AC OPERATING CONDITIONS Parameter Input High (Logic 1) Voltage, DQ, DQS and DM signals Input Low (Logic 0) Voltage, DQ, DQS and DM signals Input Differential Voltage, CK and /CK inputs Input Crossing Point Voltage, CK and /CK inputs Note: ...

Page 20

AC CHARACTERISTICS Parameter Symbol Min Row Cycle Time tRC Auto Refresh Row Cycle tRFC Time Row Active Time tRAS Active to Read with tRCD or tRAP tRASmin Auto Precharge Delay Row Address to Column tRCD Address Delay Row Active to ...

Page 21

Parameter Symbol Data-out high-impedance window 10 from CK,/CK Data-out low-impedance window 10 from CK, /CK Input Setup Time (fast slew 14,16-18 rate) Input Hold Time (fast slew 14,16-18 rate) Input Setup Time (slow slew 15-18 rate) Input Hold Time (slow ...

Page 22

Note: 1. All voltages referenced to Vss. 2. Tests for ac timing, IDD, and electrical, ac and dc characteristics, may be conducted at nominal reference/supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage ...

Page 23

The pulse duration distortion of on-chip clock circuits; and ...

Page 24

SYSTEM CHARACTERISTICS CONDITIONS for DDR SDRAMS The following tables are described specification parameters that required in systems using DDR devices to ensure proper performannce. These characteristics are for system simulation purposes and are guaranteed by design. Input Slew Rate for ...

Page 25

Note: 1. Pullup slew rate is characterized under the test conditions as shown in below Figure. Output (VOUT) 50 VSSQ 2. Pulldown slew rate is measured under the test conditions shown in below Figure. VDDQ Output (VOUT) 3. Pullup slew ...

Page 26

CAPACITANCE o (T =25 C, f=100MHz) A Parameter Input Clock Capacitance Delta Input Clock Capacitance Input Capacitance Delta Input Capacitance Input / Output Capacitance Delta Input / Output Capacitance Note: 1. VDD = min. to max., VDDQ = 2.3V to ...

Page 27

PACKAGE INFORMATION Rev. 1.0 /Nov. 2007 HY5DU561622F(L)FP 27 ...