EPF10K10 ETC, EPF10K10 Datasheet - Page 136

EPF10K10

Manufacturer Part Number

EPF10K10

Description

EMBEDDED PROGRAMMABLE LOGIC FAMILY

Manufacturer

ETC

Datasheet

1.EPF10K10.pdf

(138 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EPF10K100A3NBC356

Manufacturer:

ALTERA

Quantity:

21

Company:

Part Number:

EPF10K100ABC356-1

Manufacturer:

ALTERA

Quantity:

8 831

Company:

Part Number:

EPF10K100ABC356-1

Manufacturer:

ALTERA30

Quantity:

205

Company:

Part Number:

EPF10K100ABC356-1N

Manufacturer:

ST

Quantity:

230

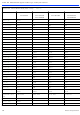

Notes to tables:

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10) To maintain pin compatibility when transferring to the EPF10K50V device from any other device in the 484-pin

(11) To maintain pin compatibility when transferring from the EPF10K100 to the EPF10K70 in the 503-pin PGA package,

(12) This pin shows the status of the ClockLock and ClockBoost circuitry. When the ClockLock and ClockBoost circuitry

(13) This pin drives the ClockLock and ClockBoost circuitry.

(14) This pin is the power or ground for the ClockLock and ClockBoost circuitry. To ensure noise resistance, the power

(15) To maintain pin compatibility when transferring to the EPF10K100A device from another device in the 600-pin BGA

136

FLEX 10K Embedded Programmable Logic Family Data Sheet

No Connect (N.C.) –

Total User I/O Pins

(8)

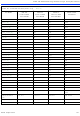

Table 122. FLEX 10K Pin-Outs (Part 3 of 3)

All pins that are not listed are user I/O pins.

This pin is a dedicated pin; it is not available as a user I/O pin.

This pin can be used as a user I/O pin if it is not used for its device-wide or configuration function.

This pin can be used as a user I/O pin after configuration.

This pin is tri-stated in user mode.

The optional JTAG pin TRST is not used in the 100-pin or 144-pin TQFP package.

To maintain pin compatibility when transferring to the EPF10K10 or EPF10K10A device from any other device in

the 208-pin PQFP or 256-pin FineLine BGA package, do not use these pins as user I/O pins.

The user I/O pin count includes dedicated input pins, dedicated clock pins, and all I/O pins.

To maintain pin compatibility when transferring to the EPF10K30 device from any other device in the 356-pin BGA

or 484-pin FineLine BGA package, do not use these pins as user I/O pins.

FineLine BGA package, do not use these pins as user I/O pins.

do not use these pins as user I/O pins.

are locked to the incoming clock and generate an internal clock, LOCK is driven high. LOCK remains high if a periodic

clock stops clocking. The LOCK function is optional; if the LOCK output is not used, this pin is a user I/O pin.

and ground supply to the ClockLock and ClockBoost circuitry should be isolated from the power and ground to the

rest of the device.

package, do not use these pins as user I/O pins.

Pin Name

406

503-Pin PGA

EPF10K100

–

470

EPF10K130V

EPF10K250A

599-Pin PGA

Note (1)

D1, D2, D3, E1, E3,

E4, E32, F1, F2, F3,

F4, G1, G2, G3, G4,

G5, H5, D33, D34,

D35, E33, E34, E35,

F32, F33, F34, G31,

G32, G33, G34, G35,

H31, AB31, AB32,

AB33, AB34, AC31,

AC32, AC33, AC34,

AC35, AD31, AD32,

AD33, AD34, AE33,

AE34, AE35, AH5,

AJ2, AJ3, AJ4, AJ5,

AK1, AK2, AK3, AK4,

AK5, AL1, AL2, AL4,

AM1, AM2, AM3

406

EPF10K100A

600-Pin BGA

(15)

–

470

Altera Corporation

EPF10K130V

EPF10K250A

600-Pin BGA