CDP6402CD HARRIS [Harris Corporation], CDP6402CD Datasheet - Page 7

CDP6402CD

Manufacturer Part Number

CDP6402CD

Description

CMOS Universal Asynchronous Receiver/Transmitter (UART)

Manufacturer

HARRIS [Harris Corporation]

Datasheet

1.CDP6402CD.pdf

(12 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

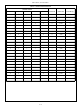

PIN

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

1

2

3

4

5

6

7

8

9

SYMBOL

RBR8

RBR7

RBR6

RBR5

RBR4

RBR3

RBR2

RBR1

TBRE

TBRL

GND

RRD

RRC

DRR

V

SFD

TRE

N/C

RRl

OE

MR

DR

PE

FE

DD

Positive Power Supply

No Connection

Ground (V

A high level on RECEIVER REGISTER DISABLE forces the receiver holding register ouputs RBR1-RBR8 to

a high impedance state.

The contents of the RECEIVER BUFFER REGISTER appear on these three-state outputs. Word formats less

than 8 characters are right justified to RBR1.

A high level on PARITY ERROR indicates that the received parity does not match parity programmed by control

bits. The output is active until parity matches on a succeeding character. When parity is inhibited, this output

is low.

A high level on FRAMING ERROR indicates the first stop bit was invalid. FE will stay active until the next valid

character’s stop bit is received.

A high level on OVERRUN ERROR indicates the data received flag was not cleared before the last character

was transferred to the receiver buffer register. The Error is reset at the next character’s stop bit if DRR has been

performed (i.e., DRR; active low).

A high level on STATUS FLAGS DISABLE forces the outputs PE, FE, OE, DR, TBRE to a high impedance

state.

The RECEIVER REGISTER CLOCK is 16X the receiver data rate.

A low level on DATA RECEIVED RESET clears the data received output (DR), to a low level.

A high level on DATA RECEIVED indicates a character has been received and transferred to the receiver buffer

register.

Serial data on RECEIVER REGISTER INPUT is clocked into the receiver register.

A high level on MASTER RESET (MR) clears PE, FE, OE and DR, and sets TRE, TBRE, and TRO. TRE is

actually set on the first rising edge of TRC after MR goes high. MR should be strobed after power-up.

A high level on TRANSMITTER BUFFER REGISTER EMPTY indicates the transmitter buffer register has

transferred its data to the transmitter register and is ready for new data.

A low level on TRANSMITTER BUFFER REGISTER LOAD transfers data from inputs TBR1-TBR8 into the

transmitter buffer register. A low to high transition on TBRL requests data transfer to the transmitter register. If

the transmitter register is busy, transfer is automatically delayed so that the two characters are transmitted end

to end.

A high level on TRANSMITTER REGISTER EMPTY indicates completed transmission of a character including

stop bits.

See Pin 5 - RBR8

SS

)

TABLE 2. FUNCTION PIN DEFINITION

CDP6402, CDP6402C

5-80

DESCRIPTION