AD9020/PCB AD [Analog Devices], AD9020/PCB Datasheet - Page 10

AD9020/PCB

Manufacturer Part Number

AD9020/PCB

Description

10-Bit 60 MSPS A/D Converter

Manufacturer

AD [Analog Devices]

Datasheet

1.AD9020PCB.pdf

(12 pages)

AD9020

Timing

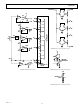

In the AD9020, the rising edge of the ENCODE signal triggers

the A/D conversion by latching the comparators. (See the

AD9020 Timing Diagram.)

The ENCODE is TTL/CMOS compatible and should be driven

from a low jitter (phase noise) source. Jitter on the ENCODE

signal will raise the noise floor of the converter. Fast, clean

edges will reduce the jitter in the signal and allow optimum ac

performance. Locking the system clock to a crystal oscillator

also helps reduce jitter. The AD9020 is designed to operate with

a 50% duty cycle; small (10%) variations in duty cycle should

not degrade performance.

Data Format

The format of the output data (D

MSB INVERT and LSBs INVERT pins. These inputs are dc

control inputs, and should be connected to GROUND or +V

The AD9020 Truth Table gives information to choose from

among Binary, Inverted Binary, Twos Complement and In-

verted Twos Complement coding.

The OVERFLOW output is an indication that the analog input

signal has exceeded the voltage at +V

overflow transition voltage and output delay are not tested or in-

cluded in the data sheet limits. Performance of the overflow in-

dicator is dependent on circuit layout and slew rate of the

encode signal. The operation of this function does not affect the

other data bits (D

requiring a critical measure of the analog input voltage.

0

–D

9

). It is not recommended for applications

ANALOG

ENCODE

OUTPUT

INPUT

DATA

0

–D

SENSE

9

) is controlled by the

. The accuracy of the

N

t

OD

AD9020 Timing Diagram

t

a

N

S

.

–10–

DATA FOR N

Layout and Power Supplies

Proper layout of high speed circuits is always critical but is par-

ticularly important when both analog and digital signals are

involved.

Analog signal paths should be kept as short as possible and be

properly terminated to avoid reflections. The analog input volt-

age and the voltage references should be kept away from digital

signal paths; this reduces the amount of digital switching noise

that is capacitively coupled into the analog section of the circuit.

Digital signal paths should also be kept short, and run lengths

should be matched to avoid propagation delay mismatch.

In high speed circuits, layout of the ground circuit is a critical

factor. A single, low impedance ground plane, on the compo-

nent side of the board, will reduce noise on the circuit ground.

Power supplies should be capacitively coupled to the ground

plane to reduce noise in the circuit. Multilayer boards allow

designers to lay out signal traces without interrupting the

ground plane and provide low impedance power planes.

It is especially important to maintain the continuity of the

ground plane under and around the AD9020. In systems with

dedicated digital and analog grounds, all grounds of the

AD9020 should be connected to the analog ground plane.

The power supplies (+V

lated from the supplies used for external devices; this further re-

duces the amount of noise coupled into the A/D converter.

Sockets limit the dynamic performance and should be used only

for prototypes or evaluation—PCK Elastomerics Part # CCS-68-

55 is recommended for the LCC package. (Tel. 215-672-0787)

An evaluation board is available to aid designers and provide a

suggested layout.

N + 1

N + 1

t

OD

t

a

– Aperture Delay

– Output Delay

S

DATA FOR N + 1

and –V

S

) of the AD9020 should be iso-

REV. A