SSM2018TS AD [Analog Devices], SSM2018TS Datasheet - Page 11

SSM2018TS

Manufacturer Part Number

SSM2018TS

Description

Trimless Voltage Controlled Amplifiers

Manufacturer

AD [Analog Devices]

Datasheet

1.SSM2018TS.pdf

(16 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

SSM2018TS

Manufacturer:

ADI/亚德诺

Quantity:

20 000

REV. A

same is true for the inverting input, which is connected to Pin 1.

The overall feedback ensures that the current flowing through

the input resistors is balanced by the collector currents in Q1

and Q4.

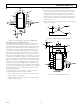

Basic VCA Configuration for the SSM2118T

The SSM2118T behaves very much in the same way as the

SSM2018T except that it has differential current outputs in-

stead of a voltage output. The basic VCA configuration is

shown in Figure 39. A dual output amplifier is needed to re-

place the internal amplifiers in the SSM2018T. However, mul-

tiple SSM2118Ts can share the output amplifiers. The op amps

are configured so that the SSM2118T’s output current is flow-

ing into a virtual ground. This same virtual ground is presented

to all the VCAs, allowing their currents to be summed without

interaction.

V

V

Figure 39. SSM2118T Typical Bus Summing Application

IN+

IN–

1 F 18k

1 F 18k

V–

–IN

+IN

V–

47pF

OPTIONAL

TRIM

10

7

6

1

2

3

4

5

6

7

8

SSM2118T

47k

47k

2

16

15

14

13

12

11

10

9

ADDITIONAL

SSM2118Ts

V–

FROM

COMP 2

COMPENSATION

V+

150k

*

FOR MORE THAN 2 SSM2118Ts

NETWORK

Figure 38. SSM2018T Detailed Functional Diagram

8

COMP 3

10k

50pF

1 F

470k

9

COMP 1

500k

*

A1

5

SYMMETRY

1k

GLOBAL

10k

TRIM

A1, A2: OP275

3k

14

18k

18k

A2

50pF

A3

V

CONTROL

–I

1–G

Im+( Is )

3

V

G

OUT

Q1

2

–11–

Q2

G

200

SPLITTER

A global symmetry trim may be necessary, but since it is at the

output amplifiers, only one trim is needed for any number of

SSM2118Ts connected to the summing bus. This trim bal-

ances the resistors around the two amplifiers. If precision,

matched resistors are used, the trim can be removed. However,

to achieve 0.006% distortion, these resistors need to be matched

to approximately 0.01%.

If the choice is made to perform the trim, then one of two meth-

ods may be used. The first method minimizes the distortion of

an audio signal with the SSM2118T in the circuit. To perform

the trim, a 0 dBu, 1 kHz sine wave is applied to one of the

VCAs, and the output distortion is monitored. As the symmetry

trim is adjusted, the output distortion will vary. The optimal

adjustment produces the lowest distortion over the entire trim

range. The second method is to insert a common mode signal

by connecting two 47 k resistors (matched to 0.01%) to the

inverting inputs of each amplifier, as shown in the Figure 39.

The signal is typically a 0 dBu, 1 kHz sine wave, although other

signals can be used. The output is monitored with an oscillo-

scope, and the potentiometer is adjusted to achieve a minimum

output signal.

The SSM2118T has the exact same input and gain core con-

struction as the SSM2018T. Thus, any discussion of these por-

tions of the SSM2018T apply equally to the SSM2118T. The

main difference, which is apparent by comparing Figure 40 to

Figure 38, is the removal of two output amplifiers, A1 and A3.

Instead, the output currents come directly from the collectors of

Q2 and Q3. Notice that the two external amplifiers in Figure

39 are configured the same as the internal amplifiers in the

SSM2018T.

Two important characteristics of these current outputs must be

considered: the output compliance and the effects of capacitive

loading. Normally, the outputs are connected to a virtual

ground node at the summing stage, which is biased at ground.

This bias point can be altered somewhat. The part maintains

good distortion performance for an output compliance from

A1

G

Q3

+I

Q4

1

Im–( Is )

1-G

1–G

2

GAIN

CORE

A2

200

V

Im

REF

1.8k

SSM2018T/SSM2118T

A4

A4

15

16

11

13

12

4

BAL

–I

V

GND

MODE

V

C

1-G

1-G