AM29PDLI27H SPANSION [SPANSION], AM29PDLI27H Datasheet

AM29PDLI27H

Related parts for AM29PDLI27H

AM29PDLI27H Summary of contents

Page 1

Am29PDL127H Data Sheet Continuity of Specifications Continuity of Ordering Part Numbers For More Information Publication Number 26864 Revision A Amendment +4 Issue Date June 30, 2003 ...

Page 2

THIS PAGE LEFT INTENTIONALLY BLANK. ...

Page 3

ADVANCE INFORMATION Am29PDL127H 128 Megabit ( 16-Bit) CMOS 3.0 Volt-only, Page Mode Simultaneous Read/Write Flash Memory with Enhanced VersatileIO DISTINCTIVE CHARACTERISTICS ARCHITECTURAL ADVANTAGES 128 Mbit Page Mode device — Page size of 8 words: Fast page read access ...

Page 4

GENERAL DESCRIPTION The Am29PDL127H is a 128 Mbit, 3.0 volt-only Page Mode and Simultaneous Read/Write Flash memory device orga- nized as 8 Mwords. The device is offered in a 64-ball Forti- fied BGA ...

Page 5

TABLE OF CONTENTS Product Selector Guide . . . . . . . . . . . . . . . . . . . . . 5 Block Diagram . . . ...

Page 6

Figure 21. DQ2 vs. DQ6.................................................................. 56 Temporary Sector Unprotect .................................................. 57 Figure 22. Temporary Sector Unprotect Timing Diagram ............... 57 Figure 23. Sector/Sector Block Protect and Unprotect Timing Diagram .............................................................. 58 Alternate CE# ...

Page 7

PRODUCT SELECTOR GUIDE Part Number 2.7–3 2.7–3 Speed Option V = 2.7–3 1.65–1. Max Access ...

Page 8

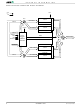

SIMULTANEOUS OPERATION BLOCK DIAGRAM Mux A22–A0 RY/BY# A22–A0 RESET# STATE WE# CONTROL CE# & WP#/ACC COMMAND REGISTER DQ0–DQ15 A22–A0 Mux ...

Page 9

CONNECTION DIAGRAMS A22 A13 A12 WE# RESET RY/BY# WP#/ACC ...

Page 10

CONNECTION DIAGRAMS A22 A7 B7 A13 A12 WE# RESET RY/BY# WP#/ACC A17 ...

Page 11

PIN DESCRIPTION A22–A0 = 23-bit address bus for 128 Mb de- vice. A9 supports 12 V autoselect in- puts. DQ15–DQ0 = 16-bit data inputs/outputs/float CE# = Chip Enable Inputs OE# = Output Enable ...

Page 12

ORDERING INFORMATION Standard Products AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the following: Am29PDL127 DEVICE ...

Page 13

DEVICE BUS OPERATIONS This section describes the requirements and use of the device bus operations, which are initiated through the internal command register. The command register itself does not occupy any addressable memory ...

Page 14

cess has access time ACC CE selects the device and OE# is the output control and should be used to gate data to the output inputs if the device ...

Page 15

(Note that this is a more restricted voltage range than CE# and RESET# are held ± 0.3 V, the device will be in the standby mode, ...

Page 16

Table 4. Am29PDL127H Sector Architecture Bank Sector SA0 SA1 SA2 SA3 SA4 SA5 SA6 SA7 SA8 SA9 SA10 SA11 SA12 SA13 SA14 SA15 SA16 SA17 SA18 SA19 SA20 SA21 SA22 SA23 SA24 SA25 ...

Page 17

Table 4. Am29PDL127H Sector Architecture Bank Sector SA39 SA40 SA41 SA42 SA43 SA44 SA45 SA46 SA47 SA48 SA49 SA50 SA51 SA52 SA53 SA54 SA55 SA56 SA57 SA58 SA59 SA60 SA61 SA62 SA63 SA64 ...

Page 18

Table 4. Am29PDL127H Sector Architecture Bank Sector SA79 SA80 SA81 SA82 SA83 SA84 SA85 SA86 SA87 SA88 SA89 SA90 SA91 SA92 SA93 SA94 SA95 SA96 SA97 SA98 SA99 SA100 SA101 SA102 SA103 SA104 ...

Page 19

Table 4. Am29PDL127H Sector Architecture Bank Sector SA119 SA120 SA121 SA122 SA123 SA124 SA125 SA126 SA127 SA128 SA129 SA130 SA131 SA132 SA133 SA134 SA135 SA136 SA137 SA138 SA139 SA140 SA141 SA142 SA143 SA144 ...

Page 20

Table 4. Am29PDL127H Sector Architecture Bank Sector SA159 SA160 SA161 SA162 SA163 SA164 SA165 SA166 SA167 SA168 SA169 SA170 SA171 SA172 SA173 SA174 SA175 SA176 SA177 SA178 SA179 SA180 SA181 SA182 SA183 SA184 ...

Page 21

Table 4. Am29PDL127H Sector Architecture Bank Sector SA199 SA200 SA201 SA202 SA203 SA204 SA205 SA206 SA207 SA208 SA209 SA210 SA211 SA212 SA213 SA214 SA215 SA216 SA217 SA218 SA219 SA220 SA221 SA222 SA223 SA224 ...

Page 22

Table 4. Am29PDL127H Sector Architecture Bank Sector SA231 SA232 SA233 SA234 SA235 SA236 SA237 SA238 SA239 SA240 SA241 SA242 SA243 SA244 SA245 SA246 SA247 SA248 SA249 SA250 SA251 SA252 SA253 SA254 SA255 SA256 ...

Page 23

Table 5. SecSi Sector Addresses Sector Size Am29PDL127H 128 words Factory-Locked Area 64 words Customer-Lockable Area 64 words Autoselect Mode The autoselect mode provides manufacturer and de- vice identification, and sector protection ...

Page 24

Table 6. Autoselect Codes (High Voltage Method) Description CE# OE# WE# Manufacturer ID AMD Read L Cycle 1 Read Cycle 2 Read L Cycle 3 Sector Protection ...

Page 25

Table 7. Am29PDL127H Boot Sector/Sector Block Addresses for Protection/Unprotection Sector A22-A12 SA0 00000000000 SA1 00000000001 SA2 00000000010 SA3 00000000011 SA4 00000000100 SA5 00000000101 SA6 00000000110 SA7 00000000111 00000001XXX SA8-SA10 00000010XXX 00000011XXX SA11-SA14 000001XXXXX ...

Page 26

SECTOR PROTECTION The Am29PDL127H features several levels of sector protection, which can disable both the program and erase operations in certain sectors or sector groups: Persistent Sector Protection A command sector protection method ...

Page 27

switch back and forth between the protected and un- protected conditions. This allows software to easily protect sectors against inadvertent changes yet does not prevent the easy removal of protection when changes are ...

Page 28

When the device is first powered on, or comes out of a reset cycle, the PPB Lock bit set to the locked state, rather than cleared to the unlocked state. The only means ...

Page 29

Lock Bit is set by issuing the PPB Lock Bit Set com- mand. Once set the only means for clearing the PPB Lock Bit is by issuing a hardware or power-up reset. The ...

Page 30

START PLSCNT = 1 RESET Wait 4 µs No First Write Temporary Sector Cycle = 60h? Unprotect Mode Yes Set up sector address Sector Protect: Write 60h to sector address ...

Page 31

Temporary Sector Unprotect This feature allows temporary unprotection of previ- ously protected sectors to change data in-system. The Sector Unprotect mode is activated by setting the RE- SET# pin During ...

Page 32

Once the SecSi Sector is locked and verified, the sys- tem must write the Exit SecSi Sector Region com- mand sequence to return to reading and writing the remainder of the array. The ...

Page 33

Addresses Data 10h 0051h 11h 0052h 12h 0059h 13h 0002h 14h 0000h 15h 0040h 16h 0000h 17h 0000h 18h 0000h 19h 0000h 1Ah 0000h Addresses Data 1Bh 0027h 1Ch 0036h 1Dh 0000h 1Eh ...

Page 34

Addresses Data 27h 0018h 28h 0001h 29h 0000h 2Ah 0000h 2Bh 0000h 2Ch 0003h 2Dh 0007h 2Eh 0000h 2Fh 0020h 30h 0000h 31h 00FDh 32h 0000h 33h 0000h 34h 0001h 35h 0007h 36h ...

Page 35

Table 12. Primary Vendor-Specific Extended Query Addresses Data 40h 0050h 41h 0052h 42h 0049h 43h 0031h 44h 0033h 45h 000Ch 46h 0002h 47h 0001h 48h 0001h 49h 0007h 4Ah 00E7h 4Bh 0000h 4Ch ...

Page 36

COMMAND DEFINITIONS Writing specific address and data commands or se- quences into the command register initiates device op- erations. Table 13 defines the valid register command sequences. Writing incorrect address and data val- ...

Page 37

command sequence. The device continues to access the SecSi Sector region until the system issues the four-cycle Exit SecSi Sector command sequence. The Exit SecSi Sector command sequence returns the de- vice to ...

Page 38

Write Program Command Sequence Data Poll from System Embedded Program algorithm in progress Verify Data? No Increment Address Last Address? Programming Completed Note: See Table 13 for program command sequence. Figure 4. Program ...

Page 39

data from the non-erasing bank. The system can de- termine the status of the erase operation by reading DQ7, DQ6, DQ2, or RY/BY# in the erasing bank. Refer to the Write Operation Status ...

Page 40

the password when programming. There are no provisions for entering the 2-cycle unlock cycle, the password program command, and all the password data. There is no special addressing order required for programming ...

Page 41

Password Unlock Command The Password Unlock command is used to clear the PPB Lock Bit so that the PPBs can be unlocked for modification, thereby allowing the PPBs to become ac- cessible for ...

Page 42

Command Definitions Tables Table 13. Memory Array Command Definitions Command (Notes) Read (5) Reset (6) Manufacturer ID Device ID (10) Autoselect SecSi Sector Factory (Note 7) Protect (8) Sector Group Protect Verify (9) ...

Page 43

Table 14. Sector Protection Command Definitions Command (Notes) Addr Data Addr Data Addr Data Reset 1 XXX F0 SecSi Sector Entry 3 555 AA 2AA 55 SecSi Sector Exit 4 555 AA 2AA ...

Page 44

WRITE OPERATION STATUS The device provides several bits to determine the status of a program or erase operation: DQ2, DQ3, DQ5, DQ6, and DQ7. Table 15 and the following subsections describe the function ...

Page 45

RY/BY#: Ready/Busy# The RY/BY dedicated, open-drain output pin which indicates whether an Embedded Algorithm is in progress or complete. The RY/BY# status is valid after the rising edge of the final ...

Page 46

DQ2: Toggle Bit II The “Toggle Bit II” on DQ2, when used with DQ6, indi- cates whether a particular sector is actively erasing (that is, the Embedded Erase algorithm is in progress), or ...

Page 47

Status Embedded Program Algorithm Standard Mode Embedded Erase Algorithm Erase Suspended Sector Erase-Suspend- Erase Read Suspend Non-Erase Mode Suspended Sector Erase-Suspend-Program Notes: 1. DQ5 switches to ‘1’ when an Embedded Program or Embedded ...

Page 48

ABSOLUTE MAXIMUM RATINGS Storage Temperature Plastic Packages . . . . . . . . . . . . . . . –65°C to +150°C Ambient Temperature with Power Applied . . . ...

Page 49

CHARACTERISTICS CMOS Compatible Parameter Parameter Description Symbol I Input Load Current LI I A9, OE#, RESET# Input Load Current LIT I Reset Leakage Current LR I Output Leakage Current ...

Page 50

TEST CONDITIONS Device Under Test C 6.2 kΩ L Note: Diodes are IN3064 or equivalent Figure 10. Test Setup KEY TO SWITCHING WAVEFORMS WAVEFORM Don’t Care, Any Change Permitted 3.0 V 1.5 V ...

Page 51

CHARACTERISTIC Read-Only Operations Parameter JEDEC Std. Description t t Read Cycle Time (Note 1) AVAV Address to Output Delay AVQV ACC t t Chip Enable to Output Delay ELQV ...

Page 52

CHARACTERISTICS Addresses CE# OE# WE# Data RESET# RY/BY A22-A3 A2-A0 Data CE# OE# Figure 13. Page Read Operation Timings ...

Page 53

CHARACTERISTICS Hardware Reset (RESET#) Parameter JEDEC Std RESET# Pin Low (During Embedded Algorithms) t Ready to Read Mode (See Note) RESET# Pin Low (NOT During Embedded t Ready Algorithms) to Read Mode ...

Page 54

CHARACTERISTICS Erase and Program Operations Parameter JEDEC Std Description t t Write Cycle Time (Note 1) AVAV Address Setup Time AVWL AS t Address Setup Time to OE# low ...

Page 55

CHARACTERISTICS Program Command Sequence (last two cycles Addresses 555h CE# OE# WE Data RY/BY VCS Note program address program data, ...

Page 56

CHARACTERISTICS Erase Command Sequence (last two cycles Addresses 2AAh CE Data 55h RY/BY# t VCS V CC Note sector ...

Page 57

CHARACTERISTICS t WC Valid PA Addresses CE# OE WE# t WPH t DS Valid Data In WE# Controlled Write Cycle Figure 18. Back-to-back Read/Write Cycle Timings ...

Page 58

CHARACTERISTICS Addresses CE# t OEH WE# OE Valid Data DQ6/DQ2 RY/BY# Note Valid address; not required for DQ6. Illustration shows first two status cycle after command sequence, ...

Page 59

CHARACTERISTICS Temporary Sector Unprotect Parameter JEDEC Std Description t V Rise and Fall Time (See Note) VIDR Rise and Fall Time (See Note) VHH HH RESET# Setup Time for ...

Page 60

CHARACTERISTICS RESET# SA, A6, A1, A0 Sector Group Protect/Unprotect Data 60h 1 µs CE# WE# OE# * For sector protect ...

Page 61

CHARACTERISTICS Alternate CE# Controlled Erase and Program Operations Parameter JEDEC Std Description t t Write Cycle Time (Note 1) AVAV Address Setup Time AVWL Address Hold ...

Page 62

CHARACTERISTICS 555 for program 2AA for erase Addresses WE# OE# CE Data t RH RESET# RY/BY# Notes: 1. Figure indicates last two bus cycles of a ...

Page 63

ERASE AND PROGRAMMING PERFORMANCE Parameter Sector Erase Time Chip Erase Time Word Program Time Accelerated Word Program Time Chip Program Time (Note 3) Notes: 1. Typical program and erase times assume the following ...

Page 64

PHYSICAL DIMENSIONS LAA064—64-Ball Fortified Ball Grid Array package Am29PDL127H June 30, 2003 ...

Page 65

PHYSICAL DIMENSIONS VBB080—80-Ball Fine-pitch Ball Grid Array 11 package D 0.05 C (2X) INDEX MARK PIN A1 CORNER 10 TOP VIEW A A1 SIDE VIEW PACKAGE VBB 080 JEDEC N/A ...

Page 66

REVISION SUMMARY Revision A (September 30, 2002) Initial release. Revision A+1 (October 29, 2002) Distinctive Characteristics Added V option at 1.8 V and 3 V I/O to Enhanced V IO Control section. Modified ...

Page 67

Trademarks Copyright © 2003 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD logo, and combinations thereof are registered trademarks of Advanced Micro Devices, Inc. ExpressFlash is a trademark of Advanced Micro ...

Page 68

Sales Offices and Representatives North America ALABAMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...