IDT74SSTUAE32866ABFG IDT, Integrated Device Technology Inc, IDT74SSTUAE32866ABFG Datasheet

IDT74SSTUAE32866ABFG

Specifications of IDT74SSTUAE32866ABFG

Available stocks

Related parts for IDT74SSTUAE32866ABFG

IDT74SSTUAE32866ABFG Summary of contents

Page 1

CONFIGURABLE REGISTERED BUFFER FOR DDR2 Description This 25-bit 1:1 or 14-bit 1:2 configurable registered buffer is designed for 1.425V to 1.575V V DD The control inputs are LVCMOS. All outputs are 1.5-V CMOS drivers that have been optimized to ...

Page 2

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Functional Block Diagram for 1:1 Mode (Positive Logic) RESET CLK CLK V REF DCKE DODT DCS CSR D1 NOTE: 1. Disabled in 1:1 configuration. 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 ...

Page 3

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Functional Block Diagram for 1:2 Mode (Positive Logic) RESET CLK CLK V REF DCKE DODT DCS CSR OTHER CHANNELS (D2-D6, D8-D10, D12-D13) NOTE: 1. Disabled in 1:1 configuration. 25-BIT CONFIGURABLE ...

Page 4

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Pin Configurations 14 BIT 1:2 REGISTERS DCKE PPO REF GND GND DODT GND GND ...

Page 5

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 96 Ball LFBGA Package Attributes Top Marking 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 C D ...

Page 6

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Function Table RESET DCS CSR ...

Page 7

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Parity and Standby Function Table RESET DCS CSR ...

Page 8

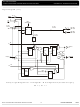

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Logic Diagram (1:1) G2 RESET H1 CLK J1 CLK D25 A3 REF PAR_IN G6 C0 Parity Logic Diagram for ...

Page 9

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Logic Diagram (1:2) G2 RESET H1 CLK J1 CLK D14 A3 REF PAR_IN G6 C0 Parity Logic Diagram for ...

Page 10

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Logic Diagram (1:2) G2 RESET H1 CLK J1 CLK D13 A3 REF PAR_IN G6 C0 Parity Logic Diagram for 1:2 Register - ...

Page 11

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Absolute Maximum Ratings Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these ...

Page 12

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Terminal Functions Terminal Name Characteristics GND REF CLK Differential Input CLK Differential Input C0, C1 RESET CSR, DCS D1 - D25 DODT DCKE Q1 - Q25 ...

Page 13

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Operating Characteristics The RESET and Cn inputs of the device must be held at valid levels (not floating) to ensure proper device operation. The differential inputs must not be floating unless RESET is ...

Page 14

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 DC Electrical Characteristics Over Operating Range Following Conditions Apply Unless Otherwise Specified: Operating Condition 0°C to +70° Symbol Parameter V IK Output HIGH Voltage Output LOW ...

Page 15

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Timing Requirements Over Recommended Operating Free-Air Temperature Range Symbol Parameter f Clock Frequency CLOCK t Pulse Duration, CLK, CLK HIGH or LOW Differential Inputs Active Time ACT 2 t Differential ...

Page 16

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Output Buffer Characteristics Output edge rates over recommended operating free-air temperature range Parameter dV/dt_r dV/dt_f 1 dV/dt_∆ 1 Difference between dV/dt_r (rising edge rate) and dV/dt_f (falling edge rate). 25-BIT CONFIGURABLE REGISTERED BUFFER ...

Page 17

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Register Timing RESET DCS CSR CLK CLK t ACT ( D25 Q1 - Q25 (1) PARIN PPO (2) QERR Timing Diagram for IDT74SSTUAE32866A Used as a Single Device ...

Page 18

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Register Timing Timing Diagram for the First IDT74SSTUAE32866A Used as a Single Device RESET Held HIGH NOTE: 1.If the data is clocked in on the n clock ...

Page 19

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Register Timing RESET (1) DCS (1) CSR (1) CLK (1) CLK ( D25 Q1 - Q25 (1) PARIN PPO QERR Timing Diagram for IDT74SSTUAE32866A Used as a Single Device ...

Page 20

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Register Timing RESET DCS CSR CLK CLK t ACT ( D14 Q1 - Q14 (1) PARIN PPO (2) QERR (not used) Timing Diagram for the First IDT74SSTUAE32866A (1:2 Register-A Configuration) Device ...

Page 21

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Register Timing Timing Diagram for the First IDT74SSTUAE32866A (1:2 Register-A Configuration) Device Used in a Pair RESET NOTE: 1.If the data is clocked in on the n ...

Page 22

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Register Timing RESET (1) DCS (1) CSR (1) CLK (1) CLK ( D14 Q1 - Q14 (1) PARIN PPO QERR (not used) Timing Diagram for the First IDT74SSTUAE32866A (1:2 Register-A Configuration) ...

Page 23

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Register Timing RESET DCS CSR CLK CLK t ACT ( D14 Q1 - Q14 (1,2) PARIN PPO (not used) (3) QERR Timing Diagram for the Second IDT74SSTUAE32866A (1:2 Register-B Configuration) Device ...

Page 24

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Register Timing Timing Diagram for the Second IDT74SSTUAE32866A (1:2 Register-B Configuration) Device Used in a Pair RESET NOTES: 1.If the data is clocked in on the n ...

Page 25

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Register Timing RESET (1) DCS (1) CSR (1) CLK (1) CLK ( D14 Q1 - Q14 (1) PARIN PPO (not used) QERR Timing Diagram for the First IDT74SSTUAE32866A (1:2 Register-A Configuration) ...

Page 26

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Test Circuits and Waveforms (V DUT CLK Out CLK Inputs CLK Test Point R 100 L = Test Point Simulation Load Circuit LVCMOS RESET Input t ...

Page 27

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Test Circuits and Waveforms (V DUT Out Load Circuit: High-to-Low Slew-Rate Adjustment Output 80% 20% dv_f dt_f Voltage Waveforms: High-to-Low Slew-Rate Adjustment DUT Out ...

Page 28

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Test Circuits and Waveforms (V DUT CLK CLK Output Load Circuit: Partial-Parity-Out Voltage Waveforms Propagation Delay Times (with respect to clock inputs) LVCMOS RESET Input Output Load Circuit: Partial-Parity-Out Voltage Waveforms Propagation Delay ...

Page 29

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Ordering Information IDT XX SSTUAE XX Family Temp. Range 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 XXX XX X Device Type Package Shipping Carrier 8 BFG 866A COMMERCIAL TEMPERATURE GRADE Tape ...

Page 30

IDT74SSTUAE32866A 25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 Innovate with IDT and accelerate your future networks. Contact: www.IDT.com For Sales 800-345-7015 408-284-8200 Fax: 408-284-2775 Corporate Headquarters Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States ...