LTC3721EGN-1#PBF Linear Technology, LTC3721EGN-1#PBF Datasheet - Page 10

LTC3721EGN-1#PBF

Manufacturer Part Number

LTC3721EGN-1#PBF

Description

IC CTLR PWM PUSH PULL HE 16SSOP

Manufacturer

Linear Technology

Datasheet

1.LTC3721EGN-1PBF.pdf

(16 pages)

Specifications of LTC3721EGN-1#PBF

Pwm Type

Current Mode

Number Of Outputs

1

Frequency - Max

1MHz

Duty Cycle

50%

Buck

No

Boost

No

Flyback

No

Inverting

No

Doubler

No

Divider

No

Cuk

No

Isolated

Yes

Operating Temperature

-40°C ~ 85°C

Package / Case

16-SSOP

Frequency-max

1MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Voltage - Supply

-

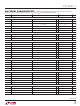

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

LTC3721-1

OPERATIO

V

ceramic capacitor to decouple the fast transient currents

demanded by the output drivers and a bulk tantalum or

electrolytic capacitor to hold up the V

bootstrap winding, or an auxiliary regulator circuit takes

over.

Regulated bias supplies as low as 7V can be utilized to

provide bias to the LTC3721-1. Refer to Figure 2 for

various bias supply configurations.

Programming Undervoltage Lockout

The LTC3721-1 provides undervoltage lockout (UVLO)

control for the input DC voltage feed to the power con-

verter in addition to the V

preceding section. Input DC feed UVLO is provided with

the UVLO pin. A comparator on UVLO compares a divided

down input DC feed voltage to the 5V precision reference.

When the 5V level is exceeded on UVLO, the SS pin is

released and output switching commences. At the same

time a 10µA current is enabled which flows out of UVLO

into the voltage divider connected to UVLO. The amount of

DC feed hysteresis provided by this current is: 10µA •

R

{(R

10

CC

TOP

C

(minimum UVLO hysteresis)

TOP

HOLDUP

should be bypassed with a 0.1µF to 1µF multilayer

, (Figure 3). The system UVLO threshold is: 5V •

+ R

12V ±10%

V

BOTTOM

CC

= (I

1.5k

ON OFF

CC

Figure 3. System UVLO Setup

Figure 2. Bias Configurations

U

+ I

)/R

1N5226

3V

1µF

DRIVE

BOTTOM

CC

) • t

UVLO function described in the

V

BIAS

}. If the voltage applied to

V

DELAY

R

< V

R

CC

TOP

BOTTOM

1N914

UVLO

V

/3.8V

IN

CC

R

START

1µF

UVLO

37211 F03

supply before the

+

C

37211 F02

HOLD

UVLO is present and greater than 5V prior to the V

circuitry activation, then the internal UVLO logic will

prevent output switching until the following three condi-

tions are met: (1) V

regulation and (3) UVLO pin is greater than 5V.

UVLO can also be used to enable and disable the power

converter. An open drain transistor connected to UVLO as

shown in Figure 3 provides this capability.

Off-Line Bias Supply Generation

If a regulated bias supply is not available to provide V

voltage to the LTC3721-1 and supporting circuitry, one

must be generated. Since the power requirement is small,

approximately 1W, and the regulation is not critical, a

simple open-loop method is usually the easiest and lowest

cost approach. One method that works well is to add a

winding to the main power transformer, and post regulate

the resultant square wave with an L-C filter (see Figure 4a).

The advantage of this approach is that it maintains decent

regulation as the supply voltage varies, and it does not

require full safety isolation from the input winding of the

transformer. Some manufacturers include a primary wind-

ing for this purpose in their standard product offerings as

well. A different approach is to add a winding to the output

inductor and peak detect and filter the square wave signal

(see Figure 4b). The polarity of this winding is designed so

Figure 4a. Auxiliary Winding Bias Supply

V

V

Figure 4b. Output Inductor Bias Supply

IN

CC

R

START

1µF

CC

15V*

ISO BARRIER

*OPTIONAL

UVLO is enabled, (2) V

C

R

HOLD

START

+

V

L

IN

OUT

C

HOLD

2k

19211 F04a

+

19211 F04b

V

V

CC

OUT

1µF

sn37211 37211fs

REF

CC

UVLO

is in

CC