NCP1378DR2G ON Semiconductor, NCP1378DR2G Datasheet

NCP1378DR2G

Specifications of NCP1378DR2G

NCP1378DR2GOS

NCP1378DR2GOSTR

Available stocks

Related parts for NCP1378DR2G

NCP1378DR2G Summary of contents

Page 1

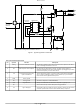

... PIN CONNECTIONS Dmg GND 4 (Top View) ORDERING INFORMATION Device Package NCP1378DR2G SOIC- -8 (Pb- -Free) NCP1378PG PDIP- -7 (Pb- -Free) †For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. 1 MARKING DIAGRAMS ...

Page 2

OVP and + Demag Universal Network *Please refer to the application information section. PIN FUNCTION DESCRIPTION Pin Symbol Function 1 Demag Core reset detection and OVP 2 FB Sets the peak current setpoint 3 CS Current sense input and skip ...

Page 3

HV PON 8.4 V 7.5 V 5.6 V (Fault) Fault To Internal Mngt. Supply GND *S and R are level triggered whereas S is edge triggered. R has priority over the other ...

Page 4

ELECTRICAL CHARACTERISTICS unless otherwise noted.) Characteristic SUPPLY SECTION V Increasing Level at which the Current Source Turns- -Off CC Minimum Operating Voltage after Turn- -On V Excursion between VCC and VCC Decreasing Level at which the Latchoff ...

Page 5

TEMPERATURE (C) Figure 3. V Threshold versus Temperature CCON 1.6 1.4 1.2 1.0 0.8 0.6 0 TEMPERATURE (C) Figure 5. Current Consumption ...

Page 6

TEMPERATURE (C) Figure 9. Drive Source Resistance versus Temperature 120 100 - TEMPERATURE (C) Figure 11. Demagnetization ...

Page 7

INTRODUCTION The NCP1378 implements a standard current mode architecture where the switch- - off time is dictated by the peak current setpoint, whereas the core reset detection triggers the turn event . This component represents the ideal candidate ...

Page 8

Once the power supply has started, the Vcc shall be constrained below 16 V, which is the maximum rating on pin 6. Figure 16 portrays a typical NCP1378 startup sequence with a Vcc regulated at 8.0 V. 9.0 8.4 V ...

Page 9

Drain Signal Timeout Signal Drain Signal Timeout Signal Figure 19. When the primary natural ringing becomes too low, the current sense initiates a new cycle when FB passes the skip level. An optocoupler is generally used to transfer the feedback ...

Page 10

An internal timer prevents any restart within 8.0 ms further to the driver going- - low transition. This prevents the switching frequency to exceed (1.0/T avoid false leakage inductance tripping at turn- - off. In some cases, the leakage inductance ...

Page 11

CTN NCP1378 Figure 24. A simple CTN triggers the latchoff as soon as the temperature exceeds a given setpoint. Shutting Off the NCP1378 Shutdown can easily be implemented through a simple NPN ...

Page 12

Vcc ON Figure 27. Typical Waveforms in Short Circuit Conditions Soft- -Start The NCP1378 features an internal 1.0 ms Soft- - Start to soften the constraints occurring in the power supply during startup activated during the power on ...

Page 13

Figure 28. This plot gathers waveforms captured at three different operating points Upper Plot: Free run, valley switching operation, Pout = Middle Plot: Min Toff clamps the switching frequency and selects the second valley. ...

Page 14

... S B 0.25 (0.010 SEATING PLANE - - 0.25 (0.010 *For additional information on our Pb- -Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D. PACKAGE DIMENSIONS SOIC CASE 751--07 ISSUE 0.10 (0.004 SOLDERING FOOTPRINT* 1.52 0.060 7.0 4.0 0.275 ...

Page 15

... SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner. PUBLICATION ORDERING INFORMATION LITERATURE FULFILLMENT: Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303- -675- -2175 or 800- -344- -3860 Toll Free USA/Canada Fax: 303- -675- -2176 or 800- -344- -3867 Toll Free USA/Canada Email: orderlit@onsemi ...