ADIS16255/PCBZ Analog Devices Inc, ADIS16255/PCBZ Datasheet - Page 5

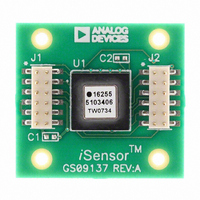

ADIS16255/PCBZ

Manufacturer Part Number

ADIS16255/PCBZ

Description

BOARD EVAL FOR ADIS16255

Manufacturer

Analog Devices Inc

Series

iMEMS®, iSensor™r

Specifications of ADIS16255/PCBZ

Sensor Type

Gyroscope, 1 Axis (Yaw Rate)

Sensing Range

±80°/sec, ±160°/sec, ±320°/sec

Interface

SPI Serial

Sensitivity

0.018°/sec/LSB

Voltage - Supply

4.75 V ~ 5.25 V

Embedded

No

Utilized Ic / Part

ADIS16255

For Use With

ADISUSBZ - KIT EVAL ADIS W/SOFTWARE USBADISEVALZ - KIT PC EVALUATION W/SOFTWARE

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ADIS16255/PCBZ

Manufacturer:

ADI/亚德诺

Quantity:

20 000

TIMING SPECIFICATIONS

T

Table 2.

Parameter

f

t

t

t

t

t

t

t

t

t

1

2

3

SCLK

DATARATE

STALL

CS

DAV

DSU

DHD

DF

DR

SFS

Guaranteed by design; not production tested.

The MSB presents an exception to this parameter. The MSB clocks out on the falling edge of CS . The rest of the DOUT bits are clocked after the falling edge of SCLK and

are governed by this specification.

This parameter may need to be expanded to allow for proper capture of the LSB. After CS goes high, the DOUT line goes into a high impedance state.

A

= −40°C to +85°C, V

DOUT

SCLK

DIN

CS

*NOT DEFINED

Description

Fast mode, SMPL_PRD ≤ 0x07 (f

Normal mode, SMPL_PRD ≥ 0x08 (f

Data rate period, fast mode, SMPL_PRD ≤ 0x07 (f

Data rate period, normal mode, SMPL_PRD ≥ 0x08 (f

Stall period, fast mode, SMPL_PRD ≤ 0x07 (f

Stall period, normal mode, SMPL_PRD ≥ 0x08 (f

Chip select to clock edge

Data output valid after SCLK falling edge

Data input setup time before SCLK rising edge

Data input hold time after SCLK rising edge

Data output fall time

Data output rise time

CS high after SCLK edge

Flash update time (power supply must be within range)

CC

t

CS

*

= 5.0 V, unless otherwise noted.

SCLK

1

MSB

CS

W/R

Figure 3. SPI Timing (Using SPI Settings Typically Identified as Phase = 1, Polarity = 1)

2

DB14

t

3

DAV

t

DSU

3

S

A5

DB13

≥ 64 Hz)

S

≤ 56.9 Hz)

Figure 2. SPI Chip Select Timing

4

t

DHD

2

A4

DB12

Rev. D | Page 5 of 20

t

DATARATE

S

≥ 64 Hz)

t

DATASTALL

S

5

S

≤ 56.9 Hz)

≥ 64 Hz)

A3

DB11

S

≤ 56.9 Hz)

6

A2

DB10

Min

0.01

0.01

32

42

9

12

48.8

24.4

48.8

5

50

D2

DB2

1

15

ADIS16250/ADIS16255

D1

DB1

Typ

5

5

16

LSB

LSB

Max

2.5

1.0

100

12.5

12.5

t

SFS

1

Unit

MHz

MHz

μs

μs

μs

μs

ns

ns

ns

ns

ns

ns

ns

ms