R5F212A8SNFP#U0 Renesas Electronics America, R5F212A8SNFP#U0 Datasheet - Page 288

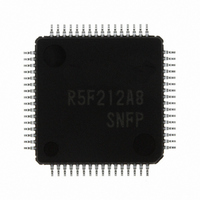

R5F212A8SNFP#U0

Manufacturer Part Number

R5F212A8SNFP#U0

Description

IC R8C/2A MCU FLASH 64LQFP

Manufacturer

Renesas Electronics America

Series

R8C/2x/2Ar

Specifications of R5F212A8SNFP#U0

Core Processor

R8C

Core Size

16/32-Bit

Speed

20MHz

Connectivity

I²C, LIN, SIO, SSU, UART/USART

Peripherals

POR, PWM, Voltage Detect, WDT

Number Of I /o

55

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

3K x 8

Voltage - Supply (vcc/vdd)

2.2 V ~ 5.5 V

Data Converters

A/D 12x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

64-LQFP

For Use With

R0K5212D8S001BE - KIT STARTER FOR R8C/2DR0K5212D8S000BE - KIT DEV FOR R8C/2D

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 288 of 611

- Download datasheet (7Mb)

R8C/2A Group, R8C/2B Group

Rev.2.00

REJ09B0324-0200

Figure 14.85

Timer RD Start Register

Timer RD Mode Register

b7 b6 b5 b4

NOTES:

b7 b6 b5 b4 b3 b2

NOTE:

1.

2.

3.

4.

5.

1. When selecting 0 (change the TRDGRji register output pin) by the IOj3 (j = C or D) bit in the TRDIORCi (i = 0 or 1)

Set the TRDSTR register using the MOV instruction (do not use the bit handling instruction). Refer to 14.4.12.1

TRDSTR Register of Notes on Tim er RD.

When the CSEL0 bit is set to 1, w rite 0 to the TSTART0 bit.

When the CSEL1 bit is set to 1, w rite 0 to the TSTART1 bit.

When the CSEL0 bit is set to 0 and the compare match signal (TRDIOA0) is generated, this bit is set to 0 (count

stops).

When the CSEL1 bit is set to 0 and the compare match signal (TRDIOA1) is generated, this bit is set to 0 (count

stops).

register, set the BFji bit in the TRDMR register to 0.

Nov 26, 2007

b3 b2

Registers TRDSTR and TRDMR in Output Compare Function

b1 b0

b1 b0

Bit Symbol

Bit Symbol

TSTART0

TSTART1

TRDSTR

(b7-b4)

(b3-b1)

Symbol

Symbol

TRDMR

CSEL0

CSEL1

SYNC

BFC0

BFD0

BFC1

BFD1

(1)

Page 266 of 580

—

—

TRD0 count start flag

TRD1 count start flag

TRD0 count operation

select bit

TRD1 count operation

select bit

Nothing is assigned. If necessary, set to 0.

When read, the content is 1.

Timer RD synchronous bit

Nothing is assigned. If necessary, set to 0.

When read, the content is 1.

TRDGRC0 register function select

bit

TRDGRD0 register function select

bit

TRDGRC1 register function select

bit

TRDGRD1 register function select

bit

(1)

(1)

(1)

(1)

Address

Bit Name

0137h

Address

Bit Name

0138h

(4)

(5)

0 : Count stops

1 : Count starts

0 : Count stops

1 : Count starts

0 : Count stops at the compare match w ith the

1 : Count continues after the compare match

0 : Count stops at the compare match w ith the

1 : Count continues after the compare match

TRDGRA0 register

w ith the TRDGRA0 register

TRDGRA1 register

w ith the TRDGRA1 register

0 : Registers TRD0 and TRD1

1 : Registers TRD0 and TRD1

0 : General register

1 : Buffer register of TRDGRA0 register

0 : General register

1 : Buffer register of TRDGRB0 register

0 : General register

1 : Buffer register of TRDGRA1 register

0 : General register

1 : Buffer register of TRDGRB1 register

operate independently

operate synchronously

(2)

(3)

After Reset

11111100b

Function

After Reset

00001110b

Function

14. Timers

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

—

—

Related parts for R5F212A8SNFP#U0

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: