R5F212A8SNFP#U0 Renesas Electronics America, R5F212A8SNFP#U0 Datasheet - Page 315

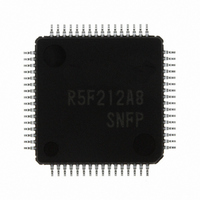

R5F212A8SNFP#U0

Manufacturer Part Number

R5F212A8SNFP#U0

Description

IC R8C/2A MCU FLASH 64LQFP

Manufacturer

Renesas Electronics America

Series

R8C/2x/2Ar

Specifications of R5F212A8SNFP#U0

Core Processor

R8C

Core Size

16/32-Bit

Speed

20MHz

Connectivity

I²C, LIN, SIO, SSU, UART/USART

Peripherals

POR, PWM, Voltage Detect, WDT

Number Of I /o

55

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

3K x 8

Voltage - Supply (vcc/vdd)

2.2 V ~ 5.5 V

Data Converters

A/D 12x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

64-LQFP

For Use With

R0K5212D8S001BE - KIT STARTER FOR R8C/2DR0K5212D8S000BE - KIT DEV FOR R8C/2D

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 315 of 611

- Download datasheet (7Mb)

R8C/2A Group, R8C/2B Group

Rev.2.00

REJ09B0324-0200

Figure 14.112 Operating Example of PWM Mode

TRDSRi register

TRDSRi register

TRDSRi register

TRDSRi register

TRDIOCi output

TRDIODi output

TRDIOBi output

The above applies under the following conditions:

Bits BFCi and BFDi in the TRDMR register are set to 0 (registers TRDGRCi and TRDGRDi are not used as buffer registers).

Bits EBi, ECi and EDi in the TRDOER1 register are set to 0 (enable TRDIOBi, TRDIOCi and TRDIODi pin outputs).

Bits TOBi and TOCi in the TRDOCR register are set to 0 (inactive level), the TODi bit is set to 1 (active level).

The POLB bit in the TRDPOCRi register is set to 1 (active level “H”), bits POLC and POLD are set to 0 (active level “L”).

i = 0 or 1

Nov 26, 2007

IMFC bit in

IMFD bit in

IMFA bit in

IMFB bit in

Count source

Value in TRDi register

1

0

1

0

1

0

1

0

m

n

p

q

to compare match

Page 293 of 580

to compare match

to compare match

Initial output “H”

Initial output “L”

Initial output “L”

Active level “H”

Active level “L”

Set to 0 by a program

Set to 0 by a program

q+1

Inactive level “H”

Inactive level “L”

p+1

n+1

m+1

m: Value set in TRDGRAi register

n: Value set in TRDGRBi register

p: Value set in TRDGRCi register

q: Value set in TRDGRDi register

m-q

Set to 0 by a program

m-p

m-n

Set to 0 by a program

14. Timers

Related parts for R5F212A8SNFP#U0

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: