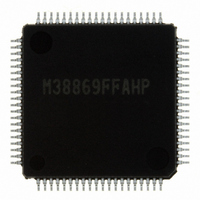

M38869FFAHP#UU Renesas Electronics America, M38869FFAHP#UU Datasheet - Page 31

M38869FFAHP#UU

Manufacturer Part Number

M38869FFAHP#UU

Description

IC 740/3886 MCU FLASH 80LQFP

Manufacturer

Renesas Electronics America

Series

740/38000r

Datasheet

1.M38869FFAGPU0.pdf

(113 pages)

Specifications of M38869FFAHP#UU

Core Processor

740

Core Size

8-Bit

Speed

10MHz

Connectivity

I²C, SIO, UART/USART

Peripherals

PWM, WDT

Number Of I /o

64

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

80-LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Fig. 24 Operation of UART serial I/O1 function

28

[Serial I/O1 Control Register (SIO1CON)]

001A

The serial I/O1 control register consists of eight control bits for the

serial I/O function.

[UART Control Register (UARTCON)] 001B

The UART control register consists of four control bits (bits 0 to 3)

which are valid when asynchronous serial I/O is selected and set

the data format of an data transfer and one bit (bit 4) which is al-

ways valid and sets the output structure of the P4

[Serial I/O1 Status Register (SIO1STS)]

0019

The read-only serial I/O1 status register consists of seven flags

(bits 0 to 6) which indicate the operating status of the serial I/O

function and various errors.

Three of the flags (bits 4 to 6) are valid only in UART mode.

The receive buffer full flag (bit 1) is cleared to “0” when the receive

buffer register is read.

If there is an error, it is detected at the same time that data is

transferred from the receive shift register to the receive buffer reg-

ister, and the receive buffer full flag is set. A write to the serial I/O1

status register clears all the error flags OE, PE, FE, and SE (bit 3

to bit 6, respectively). Writing “0” to the serial I/O1 enable bit SIOE

(bit 7 of the serial I/O control register) also clears all the status

flags, including the error flags.

Bits 0 to 6 of the serial I/O1 status register are initialized to “0” at

reset, but if the transmit enable bit (bit 4) of the serial I/O1 control

register has been set to “1”, the transmit shift completion flag (bit

2) and the transmit buffer empty flag (bit 0) become “1”.

T r a n s m i t o r r e c e i v e c l o c k

T r a n s m i t b u f f e r w r i t e

R e c e i v e b u f f e r r e a d

16

S e r i a l o u t p u t T

16

N o t e s

S e r i a l i n p u t R

1 : E r r o r f l a g d e t e c t i o n o c c u r s a t t h e s a m e t i m e t h a t t h e R B F f l a g b e c o m e s “ 1 ” ( a t 1 s t s t o p b i t , d u r i n g r e c e p t i o n ) .

2 : A s t h e t r a n s m i t i n t e r r u p t ( T I ) , w h e n e i t h e r t h e T B E o r T S C f l a g b e c o m e s “ 1 , ” c a n b e s e l e c t e d t o o c c u r d e p e n d i n g o n t h e s e t t i n g o f t h e t r a n s m i t

3 : T h e r e c e i v e i n t e r r u p t ( R I ) i s s e t w h e n t h e R B F f l a g b e c o m e s “ 1 . ”

4 : A f t e r d a t a i s w r i t t e n t o t h e t r a n s m i t b u f f e r w h e n T S C = 1 , 0 . 5 t o 1 . 5 c y c l e s o f t h e d a t a s h i f t c y c l e i s n e c e s s a r y u n t i l c h a n g i n g t o T S C = 0 .

s i g n a l

s i g n a l

i n t e r r u p t s o u r c e s e l e c t i o n b i t ( T I C ) o f t h e s e r i a l I / O 1 c o n t r o l r e g i s t e r .

X

X

D

D

T B E = 0

T S C = 0

T B E = 1

S T

S T

D

D

0

0

T B E = 0

D

D

1

5

1

/T

1 s t a r t b i t

7 o r 8 d a t a b i t

1 o r 0 p a r i t y b i t

1 o r 2 s t o p b i t ( s )

X

D pin.

16

[Transmit Buffer Register/Receive Buffer

Register (TB/RB)] 0018

The transmit buffer register and the receive buffer register are lo-

cated at the same address. The transmit buffer is write-only and

the receive buffer is read-only. If a character bit length is 7 bits, the

MSB of data stored in the receive buffer is “0”.

[Baud Rate Generator (BRG)] 001C

The baud rate generator determines the baud rate for serial trans-

fer.

The baud rate generator divides the frequency of the count source

by 1/(n + 1), where n is the value written to the baud rate genera-

tor.

R B F = 1

S P

S P

T B E = 1

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

S T

S T

D

0

D

0

MITSUBISHI MICROCOMPUTERS

R B F = 0

D

D

1

1

G e n e r a t e d a t 2 n d b i t i n 2 - s t o p - b i t m o d e

16

3886 Group

16

T S C = 1

S P

R B F = 1

S P