M30281F6HP#U3B Renesas Electronics America, M30281F6HP#U3B Datasheet - Page 284

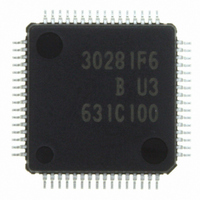

M30281F6HP#U3B

Manufacturer Part Number

M30281F6HP#U3B

Description

IC M16C/28 MCU FLASH 48K 64LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/Tiny/28r

Datasheet

1.M30280F6HPU9.pdf

(425 pages)

Specifications of M30281F6HP#U3B

Core Processor

M16C/60

Core Size

16-Bit

Speed

20MHz

Connectivity

I²C, IEBus, SIO, UART/USART

Peripherals

DMA, POR, PWM, Voltage Detect, WDT

Number Of I /o

55

Program Memory Size

48KB (48K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 13x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

64-LQFP

For Use With

R0K330290S000BE - KIT EVAL STARTER FOR M16C/29M30290T2-CPE - EMULATOR COMPACT M16C/26A/28/29M30290T2-CPE-HP - EMULATOR COMPACT FOR M16C/TINY

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M30281F6HP#U3BM30281F6HP#D5

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30281F6HP#U3BM30281F6HP#U3

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 284 of 425

- Download datasheet (4Mb)

R

R

M

16.4 I

e

E

1

. v

J

6

0

The S1D0 register controls data communication format.

16.4.1 Bits 0 to 2: Bit Counter (BC0–BC2)

16.4.2 Bit 3: I

16.4.3 Bit 4: Data Format Select Bit (ALS)

16.4.4 Bit 6: I

C

2

9

0 .

B

2 /

The BC2 to BC0 bits decide how many bits are in one byte data transferred next. After the selected

numbers of bits are transferred successfully, I

BC2 to BC0 bits are reset to "000

ACK clock), one bit for ACK clock is added to the numbers of bits selected by the BC2 to BC0 bits.

In addition, the BC2 to BC0 bits become "000

address data is transferred in 8 bits.

The ES0 bit enables to use the multi-master I

interface is disabled and the SDA and SCL pins are placed in a high-h-impedance state. When the

ES0 bit is set to “1”, the interface is enabled.

When the ES0 bit is set to “0”, the process is followed.

1)The bits in the S10 register are set as MST = "0", TRX = "0", PIN = "1", BB = "0", AL = "0", AAS = "0",

2)The S00 register cannot be written.

3)The TOF bit in the S4D0 register is set to “0” (time-out detection flag is not detected)

4)The I

The ALS bit determines whether the salve address is recognized. When the ALS bit is set to “0”, an

addressing format is selected and a address data is recognized. Only if the comparison is matched

between the slave address stored into the S0D0 register and the received address data or if the

general call is received, the data is transferred. When the ALS bit is set to "1", the free data format is

selected and the slave address is not recognized.

The IHR bit is used to reset the I

When the ES0 bit in the S1D0 register is set to“1” (I

by writing “1” to the IHR bit. Flags are processed as follows:

1)The bits in the S10 register are set as MST = "0", TRX = "0", PIN to "1", BB = "0", AL = "0", AAS =

2)The TOF bit in the S4D0 register is set to “0” (time-out detection flag is not detected)

3)The internal counter and flags are reset.

The I

matically by writing "1" to the IHR bit. Figure 16.10 shows the reset timing.

0

0

8

ADR0 = "0"

"0", and ADR0 = "0"

0

4

J

G

2

7

a

C0 Control Register 0 (S1D0)

2

o r

0 -

. n

C bus interface circuit is reset after 2.5 V

2

u

2

3

C system clock (V

0

p

, 1

0

(

M

2

0

1

0

6

7

2

2

C

C Interface Enable Bit (ES0)

C bus Interface Reset Bit (IHR)

2 /

page 262

, 8

M

1

6

IIC

C

f o

2 /

) stops counting while the internal counter and flags are reset.

8

3

) B

8

2

5

2

". At this time, if the ACK-CLK bit in the S20 register is set to "1" (with

C bus interface circuit when the error communication occurs.

2

2

" even though the START condition is detected and the

C bus interface. When the ES0 bit is set to “0”, I

2

C bus interface interrupt request is gnerated and the

IIC

2

cycles or less, and the IHR bit becomes "0" auto-

C bus interface is enabled), the hardware is reset

16. MULTI-MASTER I

2

C bus INTERFACE

2

C bus

Related parts for M30281F6HP#U3B

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: