X4323S8I Intersil, X4323S8I Datasheet - Page 10

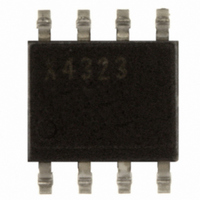

X4323S8I

Manufacturer Part Number

X4323S8I

Description

IC CPU SUPRV 32K EE RST LO 8SOIC

Manufacturer

Intersil

Type

Simple Reset/Power-On Resetr

Datasheet

1.X4323S8.pdf

(22 pages)

Specifications of X4323S8I

Number Of Voltages Monitored

1

Output

Open Drain or Open Collector

Reset

Active Low

Reset Timeout

100 ms Minimum

Voltage - Threshold

4.38V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

8-SOIC

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

X4323S8I

Manufacturer:

Intersil

Quantity:

1 550

Company:

Part Number:

X4323S8I-2.7

Manufacturer:

Intersil

Quantity:

284

Serial Start Condition

All commands are preceded by the start condition,

which is a HIGH to LOW transition of SDA when SCL

is HIGH. The device continuously monitors the SDA

and SCL lines for the start condition and will not

respond to any command until this condition has been

met. See Figure 6.

Figure 6. Valid Start and Stop Conditions

Serial Acknowledge

Acknowledge is a software convention used to indi-

cate successful data transfer. The transmitting device,

either master or slave, will release the bus after trans-

mitting eight bits. During the ninth clock cycle, the

receiver will pull the SDA line LOW to acknowledge

that it received the eight bits of data. Refer to Figure 7.

The device will respond with an acknowledge after

recognition of a start condition and if the correct

Device Identifier and Select bits are contained in the

Slave Address Byte. If a write operation is selected,

the device will respond with an acknowledge after the

receipt of each subsequent eight bit word. The device

Figure 7. Acknowledge Response from Receiver

from Receiver

Data Output

Data Output

SCL from

SCL

SDA

Master

from

10

Start

Start

1

X4323, X4325

Serial Stop Condition

All communications must be terminated by a stop con-

dition, which is a LOW to HIGH transition of SDA when

SCL is HIGH. The stop condition is also used to place

the device into the Standby power mode after a read

sequence. A stop condition can only be issued after the

transmitting device has released the bus. See Figure 6.

will acknowledge all incoming data and address bytes,

except for the Slave Address Byte when the Device

Identifier and/or Select bits are incorrect.

In the read mode, the device will transmit eight bits of

data, release the SDA line, then monitor the line for an

acknowledge. If an acknowledge is detected and no

stop condition is generated by the master, the device

will continue to transmit data. The device will terminate

further data transmissions if an acknowledge is not

detected. The master must then issue a stop condition

to return the device to Standby mode and place the

device into a known state.

8

Stop

Acknowledge

9

May 25, 2006

FN8122.1