SI4030-A0-FM Silicon Laboratories Inc, SI4030-A0-FM Datasheet - Page 5

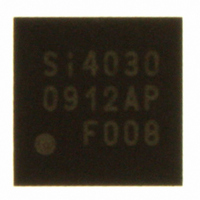

SI4030-A0-FM

Manufacturer Part Number

SI4030-A0-FM

Description

IC TX ISM 930MHZ 3.6V 20-QFN

Manufacturer

Silicon Laboratories Inc

Type

ISM Transmitterr

Specifications of SI4030-A0-FM

Package / Case

20-QFN

Frequency

240MHz ~ 930MHz

Modulation Or Protocol

FSK, GFSK, OOK

Data Rate - Maximum

128kbps

Power - Output

20dBm (100mW)

Current - Transmitting

28mA

Data Interface

PCB, Surface Mount

Antenna Connector

PCB, Surface Mount

Voltage - Supply

1.8 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Operating Frequency

240 MHz to 960 MHz

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Supply Current

100 nA

Supply Voltage (max)

3.6 V

Supply Voltage (min)

1.8 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Applications

-

Memory Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

336-1624-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SI4030-A0-FM

Manufacturer:

SILICON

Quantity:

120

Part Number:

SI4030-A0-FM

Manufacturer:

SILICONLABS/芯科

Quantity:

20 000

Si4330-B1

L

F

I S T OF

IGURES

Figure 1. RX Application Example............................................................................................ 14

Figure 2. SPI Timing.................................................................................................................. 16

Figure 3. SPI Timing—READ Mode ..........................................................................................17

Figure 4. SPI Timing—Burst Write Mode .................................................................................. 17

Figure 5. SPI Timing—Burst Read Mode .................................................................................. 17

Figure 6. State Machine Diagram.............................................................................................. 18

Figure 7. RX Timing .................................................................................................................. 22

Figure 8. Sensitivity at 1% PER vs. Carrier Frequency Offset .................................................. 26

Figure 9. PLL Synthesizer Block Diagram................................................................................. 30

Figure 10. FIFO Threshold ........................................................................................................32

Figure 11. Packet Structure....................................................................................................... 33

Figure 12. Required RX Packet Structure with Packet Handler Disabled ................................. 33

Figure 13. Multiple Packets in RX Packet Handler.................................................................... 34

Figure 14. Multiple Packets in RX with CRC or Header Error ................................................... 34

Figure 15. Operation of Data Whitening, Manchester Encoding, and CRC .............................. 36

Figure 16. Manchester Coding Example ...................................................................................36

Figure 17. Header ..................................................................................................................... 38

Figure 18. POR Glitch Parameters............................................................................................ 40

Figure 19. General Purpose ADC Architecture ......................................................................... 42

Figure 20. Temperature Ranges using ADC8 ........................................................................... 44

Figure 21. WUT Interrupt and WUT Operation.......................................................................... 47

Figure 22. Low Duty Cycle Mode .............................................................................................. 48

Figure 23. RSSI Value vs. Input Power..................................................................................... 51

Figure 24. Receiver—Schematic Receiver—Top...................................................................... 52

Figure 25. 20-Pin Quad Flat No-Lead (QFN) ............................................................................60

Figure 26. PCB Land Pattern .................................................................................................... 61

Rev 1.0

5