KSZ8841-16MBL Micrel Inc, KSZ8841-16MBL Datasheet - Page 41

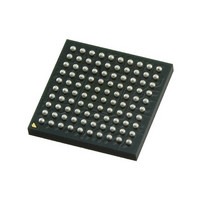

KSZ8841-16MBL

Manufacturer Part Number

KSZ8841-16MBL

Description

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer

Micrel Inc

Datasheet

1.KSZ8841-16MBL.pdf

(105 pages)

Specifications of KSZ8841-16MBL

Controller Type

Ethernet Controller, MAC

Interface

Bus

Voltage - Supply

3.1 V ~ 3.5 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

100-LFBGA

Operating Supply Voltage (typ)

3.3V

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

100

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Supply

-

Lead Free Status / Rohs Status

Compliant

Other names

576-3075

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

KSZ8841-16MBL

Manufacturer:

MICREL/麦瑞

Quantity:

20 000

The format for ConfigParam is shown in Table 10.

October 2007

Micrel, Inc.

Bit

15

14

13

12

11

10

9

8-2

1

0

Bit Name

Reserved

NO_SRST

Reserved

PME_D2

PME_D1

D2_SUP

D1_SUP

Reserved

Clock_Rate

ASYN_8bit

Description

Reserved

No Soft Reset

When this bit is set, indicates that KSZ8841M transitioning from D3_hot to D0 because

of PowerState commands do not perform an internal reset. Configuration Context is

preserved. Upon transition from the D3_hot to the D0 Initialized state, no additional

operating system intervention is required to preserve Configuration Context beyond

writing the PowerState bits.

When this bit is clear, KSZ8841M performs an internal reset upon transitioning from

D3_hot to D0 via software control of the PowerState bits. Configuration Context is lost

when performing the soft reset. Upon trasition from the D3_hot to the D0 state, full

reinitialization sequence is needed to return the device to D0 Initialized.

Regardless of this bit, devices that transition from D3_hot to D0 by a system or bus

segment reset will return to the device state D0 Uninitialized with only PME context

preserved if PME is supported and enabled.

This bit is loaded to bit 3 of PMCS register

Reserved.

PME Support D2

When this bit is set, the KSZ8841M asserts PME event (pin 14) when the KSZ8841M is

in D2 state and PME_EN is set. Otherwise, the KSZ8841M does not assert PME event

when the KSZ8841M is in D2 state.

This bit is loaded to bit 13 of PMCR register

PME Support D1

When this bit is set, the KSZ8841M asserts PME event (pin 14) when the KSZ8841M is

in D1 state and PME_EN is set. Otherwise, the KSZ8841M does not assert PME event

when the KSZ8841M is in D1 state.

This bit is loaded to bit 12 of PMCR register.

D2 Support

When this bit is set, the KSZ8841M supports D2 power state. This bit is loaded to bit 10

of PMCR register.

D1 Support

When this bit is set, the KSZ8841M supports D1 power state. This bit is loaded to bit 9

of PMCR register.

Reserved.

Internal clock rate selection

0: 125 MHz

1: 25 MHz

Note: At power up, this chip operates on 125 MHz clock. The internal frequency can be

dropped to 25 MHz via the external EEPROM.

Async 8-bit bus select

1= bus is configured for 16-bit width

0= bus is configured for 8-bit width

This bit is loaded to bit 0 of PMCR register

(32-bit width, KSZ8841-32MQL, don’t care this bit setting)

Table 10. ConfigParam Word in EEPROM Format

41

KSZ8841-16/32 MQL/MVL/MBL

M9999-102207-1.6