KSZ8851-16MLL TR Micrel Inc, KSZ8851-16MLL TR Datasheet - Page 53

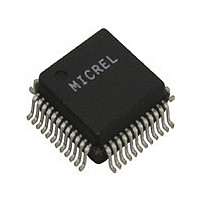

KSZ8851-16MLL TR

Manufacturer Part Number

KSZ8851-16MLL TR

Description

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer

Micrel Inc

Datasheet

1.KSZ8851-16MLL_TR.pdf

(79 pages)

Specifications of KSZ8851-16MLL TR

Operating Supply Voltage (typ)

3.3V

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

48

Lead Free Status / RoHS Status

Compliant

TX Frame Data Pointer Register (0x84 – 0x85): TXFDPR

The value of this register determines the address to be accessed within the TXQ frame buffer. When the AUTO increment

is set, It will automatically increment the pointer value on write accesses to the data register.

The counter is incremented by one for every byte access, by two for every word access, and by four for every double

word access.

RX Frame Data Pointer Register (0x86 – 0x87): RXFDPR

The value of this register determines the address to be accessed within the RXQ frame buffer. When the Auto Increment

is set, it will automatically increment the RXQ Pointer on read accesses to the data register.

The counter is incremented is by one for every byte access, by two for every word access, and by four for every double

word access.

August 2009

Micrel, Inc.

5

4

3

2-1

0

Bit

15

14

13-11

10-0

Bit

15

14

0x0

0x0

0x0

-

0x0

-

0x0

-

-

0x0

Default Value

0x000

Default Value

RW

RW

WO

RW

RW

R/W

RO

RW

RO

RO

R/W

RO

RW

when the number of received bytes in RXQ buffer exceeds the threshold set in RX Data

Byte Count Threshold Register (0x8E, RXDBCT).

RXFCTE RX Frame Count Threshold Enable

When this bit is written as 1, the KSZ8851-16MLL will enable RX interrupt (bit 13 in ISR)

when the number of received frames in RXQ buffer exceeds the threshold set in RX

Frame Count Threshold Register (0x9C, RXFCT).

ADRFE Auto-Dequeue RXQ Frame Enable

When this bit is written as 1, the KSZ8851-16MLL will automatically enable RXQ frame

buffer dequeue. The read pointer in RXQ frame buffer will be automatically adjusted to

next received frame location after current frame is completely read by the host.

SDA Start DMA Access

When this bit is written as 1, the KSZ8851-16MLL allows a DMA operation from the host

CPU to access either read RXQ frame buffer or write TXQ frame buffer with CSN and

RDN or WRN signals while the CMD pin is low. All registers access are disabled except

this register during this DMA operation.

This bit must be set to 0 when DMA operation is finished in order to access the rest of

registers.

Reserved.

RRXEF Release RX Error Frame

When this bit is written as 1, the current RX error frame buffer is released.

Note: This bit is self-clearing after the frame memory is released. The software should

wait for the bit to be cleared before processing new RX frame.

Description

Reserved.

TXFPAI TX Frame Data Pointer Auto Increment

When this bit is set, the TX Frame data pointer register increments automatically on

accesses to the data register. The increment is by one for every byte access, by two for

every word access, and by four for every doubleword access.

When this bit is reset, the TX frame data pointer is manually controlled by user to access

the TX frame location.

Reserved.

TXFP TX Frame Pointer

TX Frame Pointer index to the Frame Data register for access.

This field reset to next available TX frame location when the TX Frame Data has been

enqueued through the TXQ command register.

Description

Reserved.

RXFPAI RX Frame Pointer Auto Increment

When this bit is set, the RXQ Address register increments automatically on accesses to

53

KSZ8851-16MLL/MLLI

M9999-083109-2.0