XC3SD3400A-4CSG484C Xilinx Inc, XC3SD3400A-4CSG484C Datasheet - Page 47

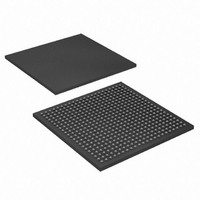

XC3SD3400A-4CSG484C

Manufacturer Part Number

XC3SD3400A-4CSG484C

Description

FPGA Spartan®-3A Family 3.4M Gates 53712 Cells 667MHz 90nm Technology 1.2V 484-Pin LCSBGA

Manufacturer

Xilinx Inc

Series

Spartan™-3A DSPr

Datasheets

1.XC3S50A-4VQG100C.pdf

(7 pages)

2.XC3SD3400A-4FGG676C.pdf

(4 pages)

3.XC3SD3400A-4FGG676C.pdf

(101 pages)

Specifications of XC3SD3400A-4CSG484C

Package

484LCSBGA

Family Name

Spartan®-3A

Device Logic Units

53712

Device System Gates

3400000

Maximum Internal Frequency

667 MHz

Typical Operating Supply Voltage

1.2 V

Maximum Number Of User I/os

309

Ram Bits

2322432

Number Of Logic Elements/cells

53712

Number Of Labs/clbs

5968

Total Ram Bits

2322432

Number Of I /o

309

Number Of Gates

3400000

Voltage - Supply

1.14 V ~ 1.26 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

484-FBGA, CSPBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

122-1532 - KIT DEVELOPMENT SPARTAN 3ADSP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

122-1540

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC3SD3400A-4CSG484C

Manufacturer:

XILINX

Quantity:

177

Company:

Part Number:

XC3SD3400A-4CSG484C

Manufacturer:

XILINX

Quantity:

110

Part Number:

XC3SD3400A-4CSG484C

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

Company:

Part Number:

XC3SD3400A-4CSG484CL

Manufacturer:

XILINX

Quantity:

123

Table 39: Switching Characteristics for the DFS

DS610 (v3.0) October 4, 2010

Product Specification

CLKOUT_DUTY_CYCLE_

FX

Notes:

1.

2.

3.

4.

5.

6.

Output Frequency Ranges

CLKOUT_FREQ_FX

Output Clock Jitter

CLKOUT_PER_JITT_FX

Duty Cycle

Phase Alignment

CLKOUT_PHASE_FX

CLKOUT_PHASE_FX180 Phase offset between the DFS CLKFX180 output and

Lock Time

LOCK_FX

The numbers in this table are based on the operating conditions set forth in

DFS performance requires the additional logic automatically added by ISE 9.1i and later software revisions.

For optimal jitter tolerance and faster lock time, use the CLKIN_PERIOD attribute.

Maximum output jitter is characterized within a reasonable noise environment (150 ps input period jitter, 40 SSOs and 25% CLB switching)

on an FPGA. Output jitter strongly depends on the environment, including the number of SSOs, the output drive strength, CLB utilization,

CLB switching activities, switching frequency, power supply and PCB design. The actual maximum output jitter depends on the system

application.

The CLKFX and CLKFX180 outputs always have an approximate 50% duty cycle.

Some duty-cycle and alignment specifications include a percentage of the CLKFX output period. For example, the data sheet specifies a

maximum CLKFX jitter of “±[1% of CLKFX period + 200]”. Assume the CLKFX output frequency is 100 MHz. The equivalent CLKFX period

is 10 ns and 1% of 10 ns is 0.1 ns or 100 ps. According to the data sheet, the maximum jitter is ±[100 ps + 200 ps] = ±300 ps.

Symbol

(2)(3)

(5)(6)

(6)

(2)

(3)(4)

Frequency for the CLKFX and CLKFX180 outputs

Period jitter at the CLKFX and

CLKFX180 outputs.

Duty cycle precision for the CLKFX and CLKFX180

outputs, including the BUFGMUX and clock tree

duty-cycle distortion

Phase offset between the DFS CLKFX output and the

DLL CLK0 output when both the DFS and DLL are used

the DLL CLK0 output when both the DFS and DLL are

used

The time from deassertion at the

DCM’s Reset input to the rising

transition at its LOCKED output. The

DFS asserts LOCKED when the

CLKFX and CLKFX180 signals are

valid. If using both the DLL and the

DFS, use the longer locking time.

Description

Spartan-3A DSP FPGA Family: DC and Switching Characteristics

www.xilinx.com

5 MHz < F

≤

> 20 MHz

< 15 MHz

F

15 MHz

CLKIN

CLKIN

CLKIN

20 MHz

Table 7

CLKIN

>

and

Device

All

All

All

All

All

All

Table

Use the Spartan-3A Jitter Calculator:

www.xilinx.com/support/documentation/

±[1% of

CLKFX

period

+ 100]

38.

Min

Typ

5

–

–

–

–

–

data_sheets/s3a_jitter_calc.zip

-5

±[1% of

±[1% of

±[1% of

CLKFX

CLKFX

CLKFX

period

+ 200]

period

+ 350]

period

+ 200]

±200

Speed Grade

Max

Max

350

450

5

±[1% of

CLKFX

period

+ 100]

Min

Typ

5

–

–

–

–

–

-4

±[1% of

±[1% of

±[1% of

CLKFX

CLKFX

CLKFX

period

+ 200]

period

+ 350]

period

+ 200]

±200

Max

Max

311

450

5

Units

MHz

ms

ps

ps

ps

ps

ps

µs

47