TR7001 RFM, TR7001 Datasheet - Page 6

TR7001

Manufacturer Part Number

TR7001

Description

RF Transceiver 3G ASH Transceiver 315 MHz 115.2 kbps

Manufacturer

RFM

Datasheet

1.TR7001.pdf

(15 pages)

Specifications of TR7001

Wireless Frequency

315 MHz

Output Power

10 mW

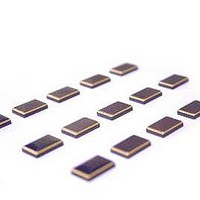

Mounting Style

SMD/SMT

Package / Case

SM3-20H

Modulation

OOK/ASK

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

DS2 is a “dB-below-peak” slicer. The peak detector charges rapidly to the

peak value of each data pulse, and decays slowly in between data pulses

(1:1000 ratio). The slicer trip point can be set from 0 to 120 mV below this

peak value with a resistor between RREF and THLD2.

DS2 is best for ASK modulation where the transmitted waveform has been

shaped to minimize signal bandwidth. However, DS2 is subject to being

temporarily “blinded” by strong noise pulses, which can cause burst data

errors. Note that DS1 is active when DS2 is used, as the compound data

slicer output is the logical AND of the DS1 and DS2 outputs. DS2 can be

disabled by leaving THLD2 disconnected. Note that a non-zero DS1

threshold is required for proper AGC operation.

Data and Clock Recovery

RXDATA is the receiver data output pin. The signal on this pin can come

from one of two sources. The default source is directly from the output of

the compound data slicer circuit. The alternate source is from the radio’s

internal data and clock recovery circuit. When the internal data and clock

recovery circuit is used (CFG0 Bit 0 high), the signal on RXDATA is

switched from the output of the data slicer to the output of the data and

clock recovery circuit when a packet start symbol is detected.

When the radio’s internal data and clock recovery circuit is not used, RXD-

CLK is a steady low value. When the internal data and clock recovery is

used, RXDCLK is low until a start symbol is detected at the output of the

data slicer. Each bit following the start symbol is output at RXDATA on the

rising edge of a RXDCLK pulse, and is stable for reading on the falling

edge of the RXDCLK pulse. Once RXDCLK is activated by the detection

of a start symbol, it remains active until CFG0 Bit 0 is reset low. Normally

RXDCLK is reset by the host processor as soon as a packet is received.

AGC Control

The output of the Peak Detector also provides an AGC Reset signal to the

AGC Control function through the AGC comparator. The purpose of the

AGC function is to extend the dynamic range of the receiver, so that two

transceivers can operate close together when running ASK and/or high

data rate modulation. The onset of saturation in the output stage of RFA1

is detected and generates the AGC Set signal to the AGC Control func-

tion. The AGC Control function then selects the 5 dB gain mode for RFA1.

The AGC Comparator will send a reset signal when the Peak Detector

output (multiplied by 0.8) falls below the threshold voltage for DS1.

Transmitter Chain

The transmitter chain consists of a SAW delay line oscillator followed by

an OOK/ASK modulated buffer amplifier. The SAW filter suppresses trans-

mitter harmonics to the antenna. Note that the same SAW devices used in

the amplifier-sequenced receiver are reused in the transmit modes.

Transmitter operation supports two modulation formats, on-off keyed

(OOK) modulation, and amplitude-shift keyed (ASK) modulation. When

OOK modulation is chosen, the transmitter output turns completely off

between “1” data pulses. When ASK modulation is chosen, a “1” pulse is

represented by a higher transmitted power level, and a “0” is represented

by a lower transmitted power level. OOK modulation provides compatibility

with first-generation ASH technology, and provides for power conserva-

tion. ASK modulation must be used for high data rates (data pulses less

than 30 µs). ASK modulation also reduces the effects of some types of

interference and allows the transmitted pulses to be shaped to control

modulation bandwidth.

When either modulation format is chosen, the receiver RF amplifiers are

turned off. In the OOK mode, the delay line oscillator amplifier TXA1 and

the buffer amplifier TXA2 are turned off when the voltage to the TXMOD

RF Monolithics, Inc.

RFM Europe

©1999 by RF Monolithics, Inc. The stylized RFM logo are registered trademarks of RF Monolithics, Inc.

Phone: (972) 233-2903

Phone: 44 1963 251383

Fax: (972) 387-8148

Fax: 44 1963 251510

input falls below 220 mV. In the OOK mode, the data rate is limited by the

turn-on and turn-off times of the delay line oscillator, which are 12 and 6 µs

respectively. In the ASK mode TXA1 is biased ON continuously, and the

output of TXA2 is modulated by the TXMOD input current. Minimum out-

put power occurs in the ASK mode when the modulation driver sinks

about 10 µA of current from the TXMOD pin.

The transmitter RF output power is proportional to the input current to the

TXMOD pin. A series resistor is used to adjust the peak transmitter output

power. +10 dBm of output power requires about 235 µA of input current.

Configuration Control

The operating configuration of the TR7001 is controlled by three pins: Pin

17 (CFGDAT), Pin 18 (CFGCLK), and Pin 19 (CFG). When DC power is

applied to the TR7001 with Pin 19 held low, the functions of Pins 17 and

18 default to the “2G ASH” TR3001 definition. This allows the TR7001 to

be used with existing TR3001 PCB layouts and protocol software. The

logic levels on Pins 17 and 18 control the default operation as shown

below:

Note that for default 2G operation, Pin 15 is grounded (zero ohm resistor)

and Pin 14 is left unconnected.

When Pin 19 is first set to a logic 1 after DC power is applied, the function-

ality of Pins 17 and 18 change from direct mode control to serial control.

This change persists until a DC power reset occurs.

After serial control is invoked, Pins 17, 18 and 19 are used to write data to

and read from three 8-bit configuration control registers in the radio. To

begin a write or read sequence, Pin 19 is set to logic 1. Data is then

clocked into or out of Pin 17 on the rising edge of each clock pulse applied

to Pin 18. Configuration data clocked into Pin 17 is transferred to a control

register every eight bits. Bits clocked into Pin 17 when Pin 19 is a logic 0

are ignored. Also, if Pin 19 is reset to logic 0 before a complete group of

eight data bits is received, the incomplete group is ignored.

Single-byte and multi-byte write and read sequences are detailed in Fig-

ures 4 and 5. The bits in the configuration registers are summarized in Fig-

ure 3.

CFG0 Bit 7 - When this bit is 0, the radio is operational. Setting this bit to 1

invokes the sleep mode. In the sleep mode most of the radio is powered

down, reducing the radio’s current consumption to about 200 nA. The con-

tents of the configuration registers are preserved during sleep mode. The

power-on default value of this bit is 0. Note that once sleep mode is

invoked, Pin 19 must be set to a logic 1 to return to active operation. In

changing from sleep mode to active mode, Pin 19 should be high for at

least one microsecond before attempting to clock data in or out of the con-

trol registers.

Pin 17

1

0

0

1

Pin 18

1

0

1

0

E-mail: info@rfm.com

http://www.rfm.com

TR7001-11062007

Transmit OOK

Transmit ASK

Receive

Mode

Sleep

Page 6 of 15