LFEC10E-3F484C LATTICE SEMICONDUCTOR, LFEC10E-3F484C Datasheet - Page 52

LFEC10E-3F484C

Manufacturer Part Number

LFEC10E-3F484C

Description

FPGA LatticeEC Family 10200 Cells 340MHz 130nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer

LATTICE SEMICONDUCTOR

Datasheet

1.LFEC3E-5TN144C.pdf

(163 pages)

Specifications of LFEC10E-3F484C

Package

484FBGA

Family Name

LatticeEC

Device Logic Units

10200

Maximum Internal Frequency

340 MHz

Typical Operating Supply Voltage

1.2 V

Maximum Number Of User I/os

288

Ram Bits

282624

In System Programmability

Yes

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFEC10E-3F484C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

- Current page: 52 of 163

- Download datasheet (962Kb)

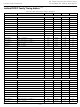

LatticeECP/EC Internal Switching Characteristics

Lattice Semiconductor

PFU/PFF Logic Mode Timing

t

t

t

t

t

t

t

t

t

t

PFU Dual Port Memory Mode Timing

t

t

t

t

t

t

t

PIC Timing

PIO Input/Output Buffer Timing

t

t

IOLOGIC Input/Output Timing

t

t

t

t

t

t

t

EBR Timing

t

t

t

t

t

t

t

t

LUT4_PFU

LUT6_PFU

LSR_PFU

SUM_PFU

HM_PFU

SUD_PFU

HD_PFU

CK2Q_PFU

LE2Q_PFU

LD2Q_PFU

CORAM_PFU

SUDATA_PFU

HDATA_PFU

SUADDR_PFU

HADDR_PFU

SUWREN_PFU

HWREN_PFU

IN_PIO

OUT_PIO

SUI_PIO

HI_PIO

COO_PIO

SUCE_PIO

HCE_PIO

SULSR_PIO

HLSR_PIO

CO_EBR

COO_EBR

SUDATA_EBR

HDATA_EBR

SUADDR_EBR

HADDR_EBR

SUWREN_EBR

HWREN_EBR

Parameter

LUT4 Delay (A to D Inputs to F Output)

LUT6 Delay (A to D Inputs to OFX Output)

Set/Reset to Output of PFU

Clock to Mux (M0,M1) Input Setup Time

Clock to Mux (M0,M1) Input Hold Time

Clock to D Input Setup Time

Clock to D Input Hold time

Clock to Q Delay, D-type Register Configuration

Clock to Q Delay Latch Configuration

D to Q Throughput Delay when Latch is Enabled

Clock to Output

Data Setup Time

Data Hold Time

Address Setup Time

Address Hold Time

Write/Read Enable Setup Time

Write/Read Enable Hold Time

Input Buffer Delay

Output Buffer Delay

Input Register Setup Time (Data Before Clock)

Input Register Hold Time (Data after Clock)

Output Register Clock to Output Delay

Input Register Clock Enable Setup Time

Input Register Clock Enable Hold Time

Set/Reset Setup Time

Set/Reset Hold Time

Clock to Output from Address or Data

Clock to Output from EBR output Register

Setup Data to EBR Memory

Hold Data to EBR Memory

Setup Address to EBR Memory

Hold Address to EBR Memory

Setup Write/Read Enable to EBR Memory

Hold Write/Read Enable to EBR Memory

Description

Over Recommended Operating Conditions

3-16

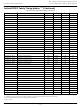

-0.05

-0.03

-0.20

-0.51

-0.24

-0.10

-0.15

-0.29

-0.29

-0.18

Min.

0.12

0.12

0.26

0.64

0.30

0.90

0.62

0.12

0.18

0.37

0.37

0.23

—

—

—

—

—

—

—

—

—

—

—

—

-5

Max.

DC and Switching Characteristics

0.25

0.40

0.81

0.36

0.48

0.50

0.36

0.56

1.92

0.33

3.64

0.74

LatticeECP/EC Family Data Sheet

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

-0.06

-0.03

-0.24

-0.62

-0.29

-0.12

-0.18

-0.35

-0.35

-0.22

Min.

0.14

0.14

0.31

0.77

0.36

1.08

0.74

0.14

0.21

0.44

0.45

0.28

—

—

—

—

—

—

—

—

—

—

—

—

-4

Max.

0.31

0.48

0.98

0.44

0.58

0.60

0.44

0.67

2.31

0.40

4.37

0.88

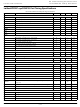

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

-0.06

-0.04

-0.28

-0.72

-0.34

-0.14

-0.21

-0.41

-0.41

-0.26

Min.

0.16

0.16

0.36

0.90

0.42

1.26

0.87

0.17

0.25

0.52

0.52

0.33

—

—

—

—

—

—

—

—

—

—

—

—

-3

Max.

0.36

0.56

1.14

0.51

0.68

0.69

0.51

0.78

2.69

0.46

5.10

1.03

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Units

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Related parts for LFEC10E-3F484C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

FPGA LatticeEC Family 10200 Cells 340MHz 130nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeEC Family 10200 Cells 340MHz 130nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeEC Family 10200 Cells 420MHz 130nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

Latticeecp/ec Family of Fpga Devices Has Been Optimized to Deliver Mainstream Fpga Features at Low Cost.for Maximum Performance And Value, The Latticeecp (EConomy Plus) Fpga Concept Combines an Efficient Fpgafabric With High-speed Dedicated Functions

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

ISPLSI2032-80LT44Lattice Semiconductor [In-System Programmable High Density PLD]

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

IC PROGRAMMED LATTICE GAL 16V8

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet: