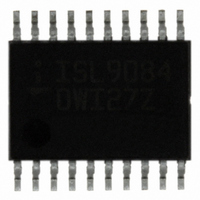

ISL90840WIV2027Z Intersil, ISL90840WIV2027Z Datasheet - Page 10

ISL90840WIV2027Z

Manufacturer Part Number

ISL90840WIV2027Z

Description

IC POT DGTL QUAD 10K OHM 20TSSOP

Manufacturer

Intersil

Series

XDCP™r

Datasheet

1.ISL90840WIV2027Z.pdf

(13 pages)

Specifications of ISL90840WIV2027Z

Taps

256

Resistance (ohms)

10K

Number Of Circuits

4

Temperature Coefficient

45 ppm/°C Typical

Memory Type

Volatile

Interface

I²C, 2-Wire Serial

Voltage - Supply

2.7 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

20-TSSOP

Resistance In Ohms

10K

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ISL90840WIV2027ZT1

Manufacturer:

INTERSIL

Quantity:

20 000

Principles of Operation

The ISL90840 is an integrated circuit incorporating four

DCPs with their associated registers, and an I

interface providing direct communication between a host

and the potentiometers.

DCP Description

Each DCP is implemented with a combination of resistor

elements and CMOS switches. The physical ends of each

DCP are equivalent to the fixed terminals of a mechanical

potentiometer (R

connected to intermediate nodes, and is equivalent to the

wiper terminal of a mechanical potentiometer. The position

of the wiper terminal within the DCP is controlled by an 8-bit

volatile Wiper Register (WR). Each DCP has its own WR.

When the WR of a DCP contains all zeroes (WR[7:0]: 00h),

its wiper terminal (R

When the WR of a DCP contains all ones (WR[7:0]: FFh), its

wiper terminal (R

the value of the WR increases from all zeroes (0 decimal) to

all ones (255 decimal), the wiper moves monotonically from

the position closest to R

time, the resistance between R

monotonically, while the resistance between R

decreases monotonically.

While the ISL90840 is being powered up, all four WRs are

reset to 80h (128 decimal), which locates R

center between R

The WRs can be read or written to directly using the I

serial interface as described in the following sections. The

I

and 03h to access the WR of DCP0, DCP1, DCP2, and

DCP3 respectively

I

The ISL90840 supports a bidirectional bus oriented protocol.

The protocol defines any device that sends data onto the

bus as a transmitter and the receiving device as the receiver.

The device controlling the transfer is a master and the

device being controlled is the slave. The master always

initiates data transfers and provides the clock for both

transmit and receive operations. Therefore, the ISL90840

operates as a slave device in all applications.

All communication over the I

sending the MSB of each byte of data first.

Protocol Conventions

Data states on the SDA line must change only during SCL

LOW periods. SDA state changes during SCL HIGH are

reserved for indicating START and STOP conditions (See

Figure 15). On power-up of the ISL90840 the SDA pin is in

the input mode.

2

2

C interface Address Byte has to be set to 00h, 01h, 02h,

C Serial Interface

H

W

L

and R

) is closest to its “High” terminal (R

and R

W

) is closest to its “Low” terminal (R

L

L

H

to the closest to R

pins). The R

.

2

10

C interface is conducted by

W

and R

W

L

pin of each DCP is

increases

W

H

. At the same

2

roughly at the

H

C serial

and R

2

H

W

C

). As

L

).

ISL90840

All I

condition, which is a HIGH to LOW transition of SDA while

SCL is HIGH. The ISL90840 continuously monitors the SDA

and SCL lines for the START condition and does not

respond to any command until this condition is met (See

Figure 15). A START condition is ignored during the power-

up of the device.

All I

condition, which is a LOW to HIGH transition of SDA while

SCL is HIGH (See Figure 15). A STOP condition at the end

of a read operation, or at the end of a write operation places

the device in its standby mode.

An acknowledge (ACK) is a software convention used to

indicate a successful data transfer. The transmitting device,

either master or slave, releases the SDA bus after

transmitting eight bits. During the ninth clock cycle, the

receiver pulls the SDA line LOW to acknowledge the

reception of the eight bits of data (See Figure 16).

The ISL90840 responds with an ACK after recognition of a

START condition followed by a valid Identification Byte, and

once again after successful receipt of an Address Byte. The

ISL90840 also responds with an ACK after receiving a Data

Byte of a write operation. The master must respond with an

ACK after receiving a Data Byte of a read operation

A valid Identification Byte contains 0101 as the four MSBs,

and the following three bits matching the logic values

present at pins A2, A1, and A0. The LSB is the Read/Write

bit. Its value is “1” for a Read operation, and “0” for a Write

operation (See Table 1).

(MSB)

0

2

2

C interface operations must begin with a START

C interface operations must be terminated by a STOP

TABLE 1. IDENTIFICATION BYTE FORMAT

1

Logic values at pins A2, A1, and A0 respectively

0

1

A2

A1

November 14, 2006

A0

FN8086.2

(LSB)

R/W