EP1S25F672C8 Altera, EP1S25F672C8 Datasheet - Page 81

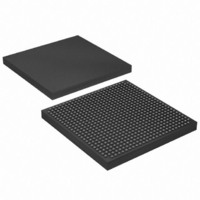

EP1S25F672C8

Manufacturer Part Number

EP1S25F672C8

Description

IC STRATIX FPGA 25K LE 672-FBGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F780C7.pdf

(276 pages)

Specifications of EP1S25F672C8

Number Of Logic Elements/cells

25660

Number Of Labs/clbs

2566

Total Ram Bits

1944576

Number Of I /o

473

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

672-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Other names

544-1119

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1S25F672C8

Manufacturer:

AD

Quantity:

2 562

Company:

Part Number:

EP1S25F672C8

Manufacturer:

ALTERA

Quantity:

3 000

Part Number:

EP1S25F672C8

Manufacturer:

ALTERA

Quantity:

20 000

Company:

Part Number:

EP1S25F672C8N

Manufacturer:

ALTERA

Quantity:

465

Part Number:

EP1S25F672C8N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 81 of 276

- Download datasheet (4Mb)

Figure 2–37. Multiply-Accumulate Mode

Notes to

(1)

(2)

Altera Corporation

July 2005

Data B

Data A

These signals are not registered or registered once to match the data path pipeline.

These signals are not registered, registered once, or registered twice for latency to match the data path pipeline.

Shiftout B Shiftout A

Figure

Shiftin B

2–37:

ENA

ENA

D

D

CLRN

CLRN

Shiftin A

Q

Q

signa (1)

signb (1)

clock

Multiply-Accumulator Mode

In multiply-accumulator mode (see

multiplied results to the adder/subtractor/accumulator block configured

as an accumulator. You can implement one or two multiply-accumulators

up to 18 × 18 bits in one DSP block. The first and third multiplier sub-

blocks are unused in this mode, because only one multiplier can feed one

of two accumulators. The multiply-accumulator output can be up to 52

bits—a maximum of a 36-bit result with 16 bits of accumulation. The

accum_sload and overflow signals are only available in this mode.

The addnsub signal can set the accumulator for decimation and the

overflow signal indicates underflow condition.

Two-Multipliers Adder Mode

The two-multipliers adder mode uses the adder/subtractor/accumulator

block to add or subtract the outputs of the multiplier block, which is

useful for applications such as FFT functions and complex FIR filters. A

ena

aclr

ENA

D

CLRN

Q

accum_sload (2)

addnsub (2)

signa (2)

signb (2)

Figure

Accumulator

Stratix Device Handbook, Volume 1

2–37), the DSP block drives

ENA

D

CLRN

Stratix Architecture

Q

Data Out

overflow

2–67

Related parts for EP1S25F672C8

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: